# Characterisation And Implementation Of HV-CMOS For High Radiation Environments

### **Benjamin Wade**

Supervisors: E. Vilella-Figueras

J. Vossebeld

Christmas Meeting 2nd Year

### HV-CMOS Motivations And Such

Placed close to collision center

Sensors receive high radiation dose

Fine spatial resolution required

Good time resolution

High rate of events MHz-GHz rate of bunch crossings

Minimal track disruption

Higher collision energies

- Thin sensors

- More radiation, finer detail needed

### Sensors need to be thin, fast, radiation tolerant, and within budget

#### DISCLAIMER: I do not work for ATLAS, this is just an example

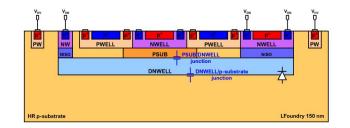

### Integrated Readout Circuitry:

- Thin sensors

- Industrial standard

- Cost effective

### High Voltage Pixel:

- More radiation tolerant

- Fast charge collection (Drift)

### HV-CMOS Motivations And Such

### UKRI Work Over The Last Year

**UKRI-MPW0**

- Characterisation of depletion region (eTCT)

- Effects of Non Ionising Energy Loss (NIEL) radiation on depletion region

- Conference proceedings published

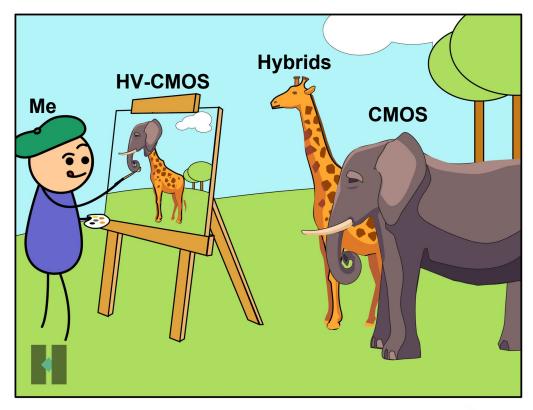

Ultimate goal:

- Improve radiation tolerance of HV-CMOS sensors

- Replace Hybrid-pixels

- TAKE OVER THE WORLD

- TCAD simulation

- Interpixel channel reduction

- Breakdown simulations

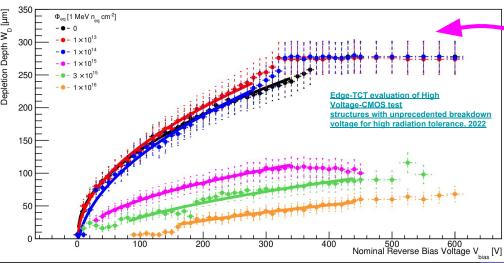

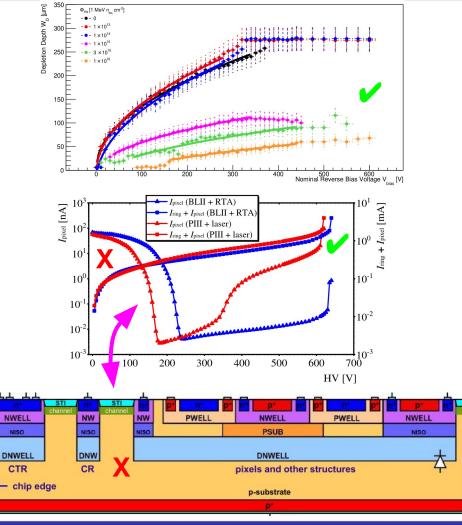

## UKRI-MPW0 Depletion Region Evaluation

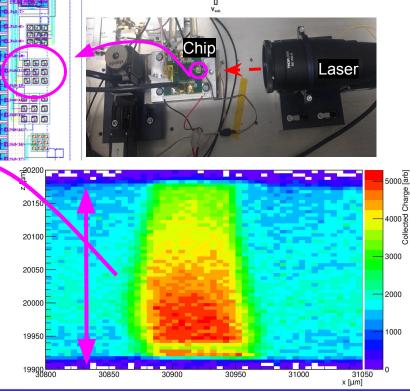

- Evaluation by edge Transient Current Technique (eTCT)

- IR laser on 3x3 passive test structure

- Beam waist penetrates generating signal in depletion region

- Move in x,y,z to map region

- Map reduction in depletion depth with radiation

- 50  $\mu$ m depletion depth at 1 x10<sup>16</sup> 1 MeV n<sub>eq</sub> cm<sup>-2</sup> (Orange line at the bottom)

Benjamin Wade

# UKRI-MPW0 To MPW1

# To Keep

### High Substrate resistivity Backside Biasing

- Breakdown Voltage ~ 600 V

Highest in field but can be increased

- 50 μm depletion depth at 1 x10<sup>16</sup> 1 MeV n<sub>eq</sub> cm<sup>-2</sup>

Down from 280 μm unirradiated... Excellent

### To Improve

Guard Ring Structure STI/Si Interface

- X High leakage current 4 mA Bad, needs reducing

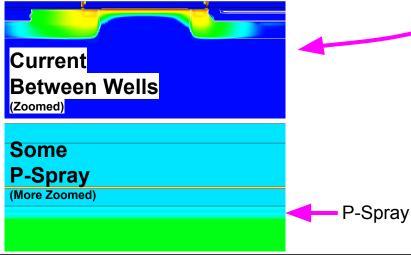

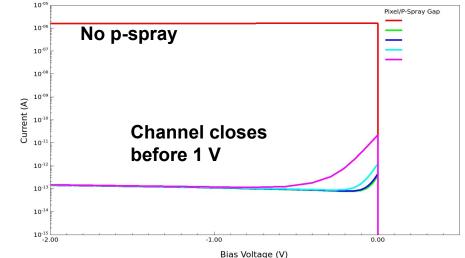

- X Current between pixels at low biases Caused by intrinsic charge on oxide insulation

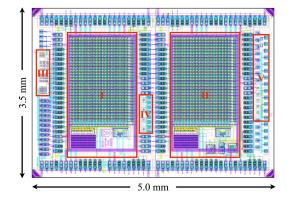

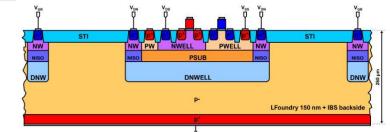

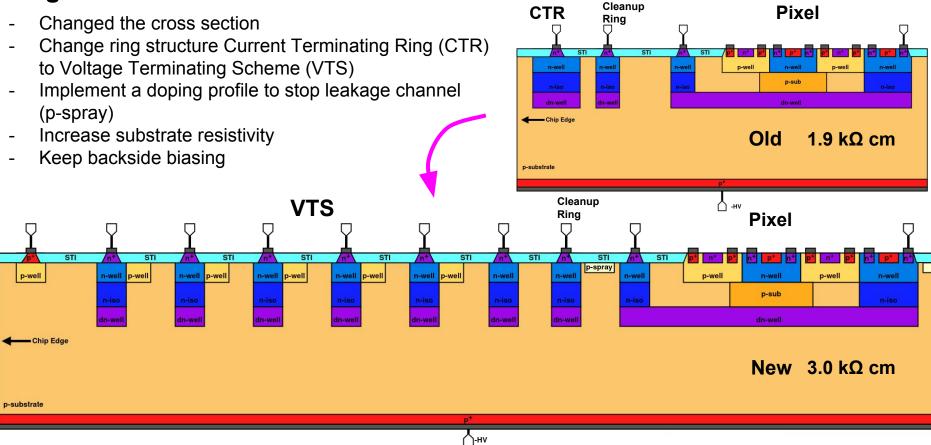

# UKRI-MPW1 Design

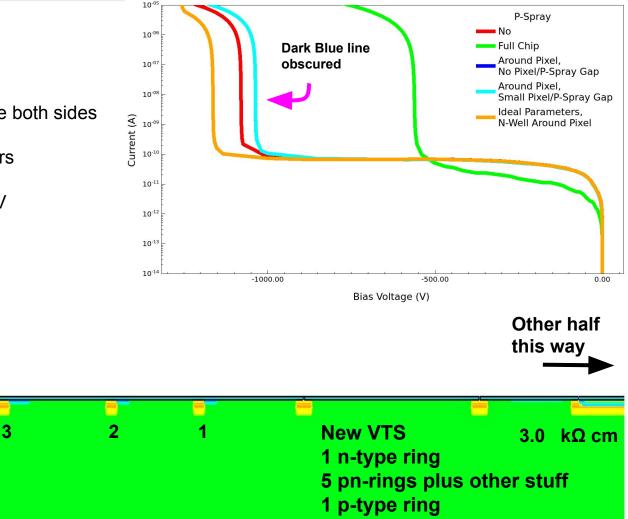

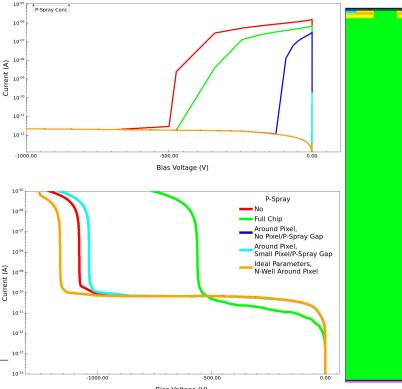

# UKRI-MPW1 TCAD

- Create and evaluate simulations for efficacy

- Done with Sentaurus Workbench, Synopsys (Using 3 to 4 different programming languages)

- Simulate current between pixels

- Apply several p-spray profiles

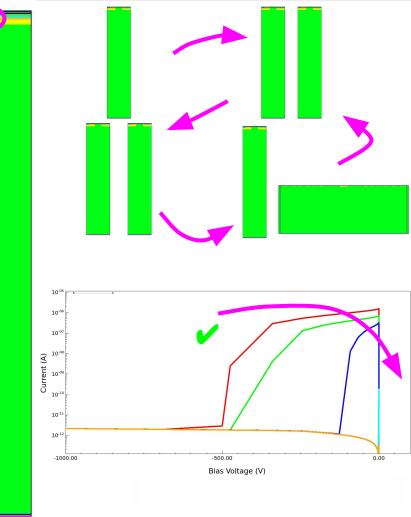

- Apply to a wider chip for effects on breakdown

- Iterate for desired current reduction and breakdown

## UKRI-MPW1 TCAD Continued

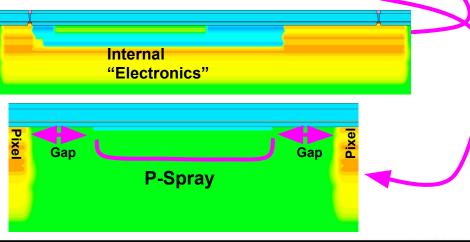

- Setup new chip

- Simulate 1 pixel and ring structure both sides

- Carefully position p-spray

- Give LFoundry p-spray parameters

- Simulations not perfect

P-type seal ring

5

n-type

Final chip design breaks ~ 1000 V (orange line)

p-type

# **Outlook**

#### <u>Done</u>

- Some measurements

- Published conference proceedings

- Some TCAD

- Gave LFoundry a new doping profile

### <u>To Do</u>

**Merry Christmas!**

- Finish characterising old chip

- Write paper on UKRI-MPW1 TCAD

- Start characterising new chip

- See how accurate simulations are

- Starts TCADing next iterations and ideas (MPW2)

Edge-TCT evaluation of high voltage-CMOS test structures with unprecedented breakdown voltage for high radiation tolerance

B. Wade,<sup>a,\*</sup> M. Franks,<sup>a,b,1</sup> J. Hammerich,<sup>a</sup> N. Karim,<sup>a,2</sup> S. Powell,<sup>a</sup> E. Vilella<sup>a</sup> and C. Zhang<sup>a</sup>

Bias Voltage (V)

## UKRI-MPW1 TCAD

- Need to see how this p-spray affects the wider breakdown of the chip itself

- Make the simulation

- Iterate through some different p-spray doping profiles

- Apply these to a "Full chip" simulation

- Can't put p-spray inside pixel

- Trial gaps between p-spray and pixel

BACKUP

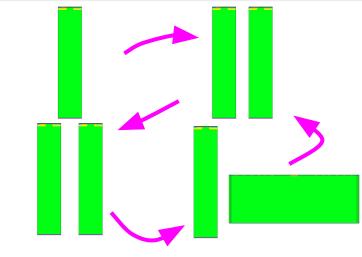

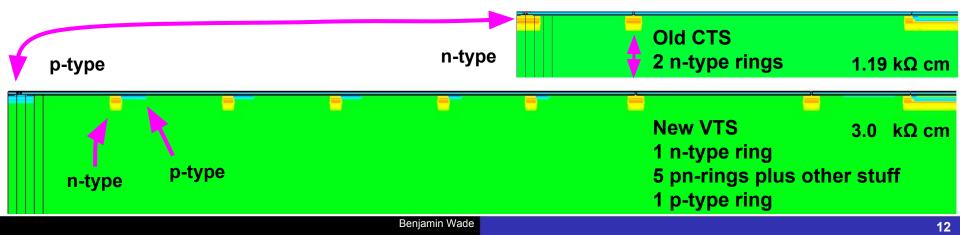

# UKRI-MPW0/MPW1 All Changes compared

- Change from Current Terminating Scheme (CTS) to Voltage Terminating Scheme (VTS)

- Old substrate resistivity 1.19 kΩ cm measured (1.9 kΩ cm nominal)

- New substrate resistivity 3.0 kΩ cm

BACKUP