# **LHCb Upgrade II**

**Particle Physics Annual Meeting**

18/19<sup>th</sup> May 2023

Eva Vilella-Figueras, **Ashley Greenall**, Jan Hammerich, Karol Hennessy, Tim Jones, Ayushi Khatri, Sigrid Scherl

## Introduction

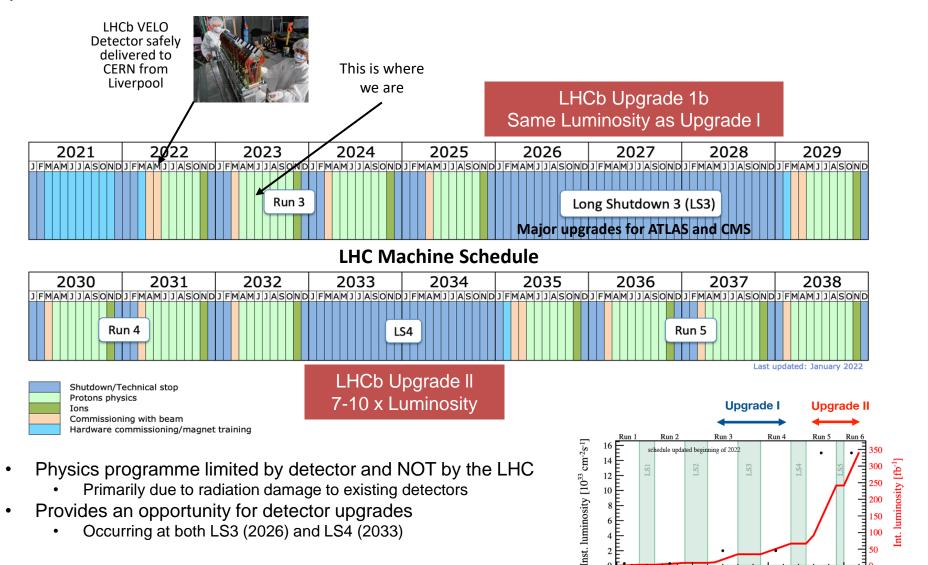

- Time-line of LHC machine

- Long Shutdowns, their occurrence and opportunity for detector upgrades

- LHCb upgrades

- Areas of interest

- Mighty Tracker

- Overview, where our interests lie and current activities

- Conclusion

### **LHCb Upgrade II: Timeline**

Liverpool positioning itself in considering exploiting these upgrades

2040

2020

2030

Year

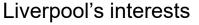

# **LHCb Upgrade II: Liverpool's Interests**

Interest shown towards 2 sub-detector systems:

- 1. Upgraded Vertex Locator still under discussion

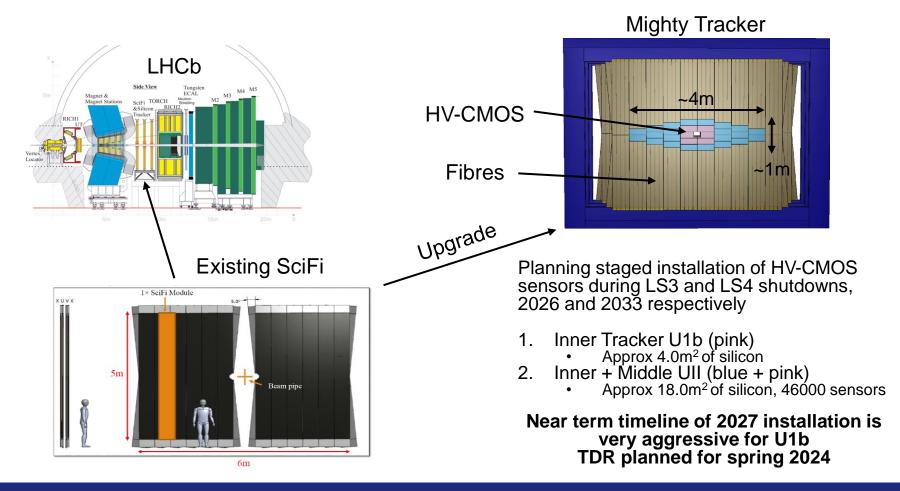

- 2. <u>Mighty Tracker</u> Activity currently aligned, a combined scintillating fibre & HV-CMOS detector (SCiFi & Silicon Tracker)

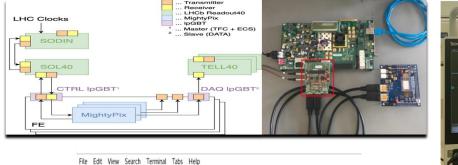

### Mighty Tracker: what is it

Mighty Tracker, made up of 2 detector systems,

- 1. Scintillating Fibres SciFi

- 2. Silicon tracker made up of a HV-CMOS detector (Liverpool's interest)

# **Mighty Tracker Liverpool Activities: ASICs**

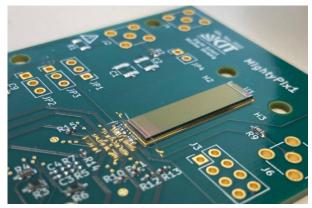

- HV-CMOS Pixel chip MightyPix

- Based on existing ATLASPix and MuPix devices

- ASIC design and verification is done by KIT at Karlsruhe, Germany

- With inputs from Liverpool

- Plus, qualification of prototype ASICs (ATLASPix3 & MuPix10) Irradiation & Testbeam studies

- First prototype chip: MightyPix1

- Chip size: 20mm x 5mm (full length column, ¼ width)

- Pixel size: 165μm x 55μm

- Time resolution: <3ns</li>

- Up to 1.28Gbs Data output rate

- Submitted as MPW (May 2022) implemented in TSI 180nm process

- Delivered Q1 2023

- Testing indicated chip is non-working

- Problem identified to a single node not being connected

- Missed at the verification stage

MightyPix1

**Courtesy of Sigrid Scherl**

# Mighty Tracker Liverpool Activities: ASICs – what next?

- MightyPix1 is very important as precursor to MightyPix2

- Exploits full reticle coming in at 20mm x 20mm

- LHCb DAQ compatible, improved radiation hardness, SEE mitigation, integrated LDOs, ...

- Evaluation of MightyPix1 analogue front-end especially important

- Timing performance, dynamic range, susceptibility to radiation damage, ...

- Feeding back into design of MightyPix2 if necessary

- MightyPix2 originally scheduled for submission Q2/Q3 2023

- Submission turnaround is typically 6 months

- Feeds into U1b TDR submission spring 2024 we're running late

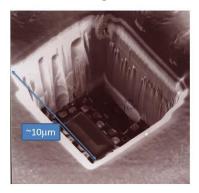

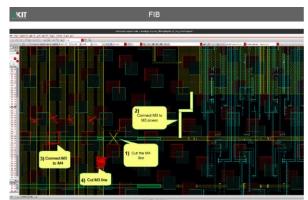

- Investigated fixing existing MightyPix1s using Focused Ion Beam (FIB)

- Can cut/add metal at the nanometer scale £1800/chip

- Has been used successfully with ATLAS prototype chips

- 3 out of 4 chips working expected yield (from vendor)

- Work undertaken very similar to that required for MightyPix1

- 5 x MightyPix1 submitted for FIB

- All returned die tested and still non-functional

- Suggestion that the re-work is non-optimal

- Pursuing companies within Europe for alternative FIB source

- ASIC program in state of flux uncertainty upon how to advance

- Hopefully will be resolved very soon

**ATLAS FIB**

Courtesy of KIT

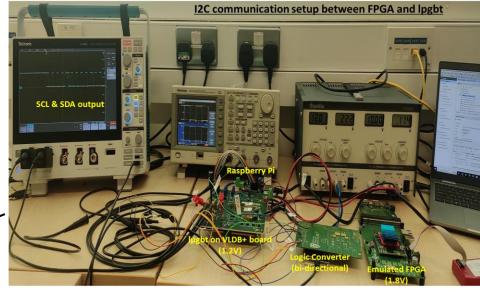

# Mighty Tracker Liverpool Activities: MightyPix1 FPGA emulation

Confirmation of working I2C link

Ayushi Khatri & Karol Hennessy

- Emulation of digital readout of MightyPix1

- ASIC design successfully simulated, synthesized and implemented on Xilinx FPGA using Vivado

- Chip configuration confirmed by scoping of output waveforms

- Have also checked out I2C communication is working used for configuration of MightyPix1

- Firstly, checking out LpGBT to VTRx+ I2C link

- CERN derived Gbit Transeiver and Optical data link

- Then successfully swapped to FPGA, emulating as MightyPix1

- No showstoppers identified

### Mighty Tracker Liverpool Activities: Modules

- Still very much at the conceptual stage

- Definition of module form-factor, topology, readout architecture, powering etc. yet to be fixed

- Expect decision to be made towards end of year

- Lack of ASICs compounds matters

- MightyPix1 initially being used as a test vehicle

- Checking out chip susceptibility to EMI from DCDC converters, data transmission, ...

- Followed by development of flex circuits and their assembly tooling using full sized chips

- Furthermore, U1b modules might not necessarily be the same as those installed at UII

- For example, Serial powering is being discussed for UII but not considered for U1b

- Progress is being made

- Taking advantage of experience gained from current ATLAS ITk builds

- Making everything as modular as possible with testability introduced at the outset

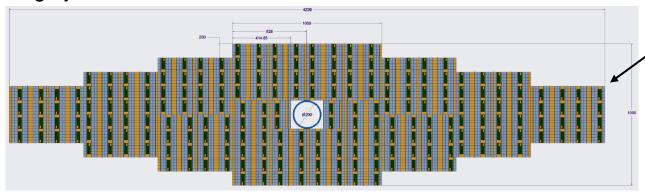

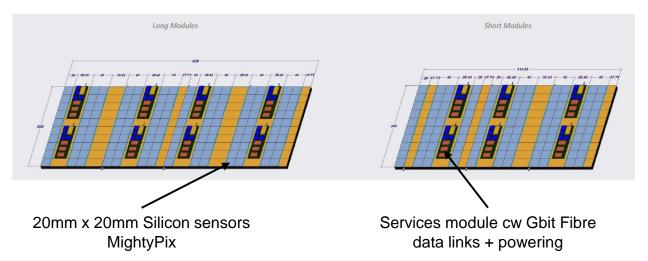

# **Mighty Tracker Liverpool Activities: Modules**

#### Mighty Tracker

Carbon fibre cores with integrated cooling

- Targeting 2 module types, predominantly Long modules with a small number of Short modules

- Short modules being used in the proximity of the beam pipe hole

#### Under discussion for U1b

- Powering, DCDC or direct

- U2 serial powering?

- Services module location

- Modularity of sensor arrays

- Whilst having no space...

#### Conclusion

- LHCb Upgrade II provides Liverpool an opportunity to participate in future detector builds

- Exploiting our expertise in ASIC & electronic design, mechanics, assembly and integration

- Taking us up to and beyond 2033

- Early days, but group are already proactive within the Mighty Tracker community

- Providing steers on both ASIC and module designs

- As usual things are not going as planned, vis: non-working ASICs

- The lack of ASICs impeding module development

- Highlights how exposed detector R&D and builds are to ASIC delivery schedules

- This is not peculiar to the Mighty Tracker

# Thank You