Design and characterisation of highspeed depleted monolithic active pixel sensor (DMAPS) detectors

### Matthew Franks

m.l.franks@liverpool.ac.uk

Supervisors: E. Vilella-Figueras<sup>1</sup>, N. Massari<sup>2</sup>, and J. Vossebeld<sup>1</sup> <sup>1</sup>University of Liverpool, UK; <sup>2</sup>Fondazione Bruno Kessler (FBK), Italy

> HEP Annual Meeting Thursday, 19<sup>th</sup> December 2019

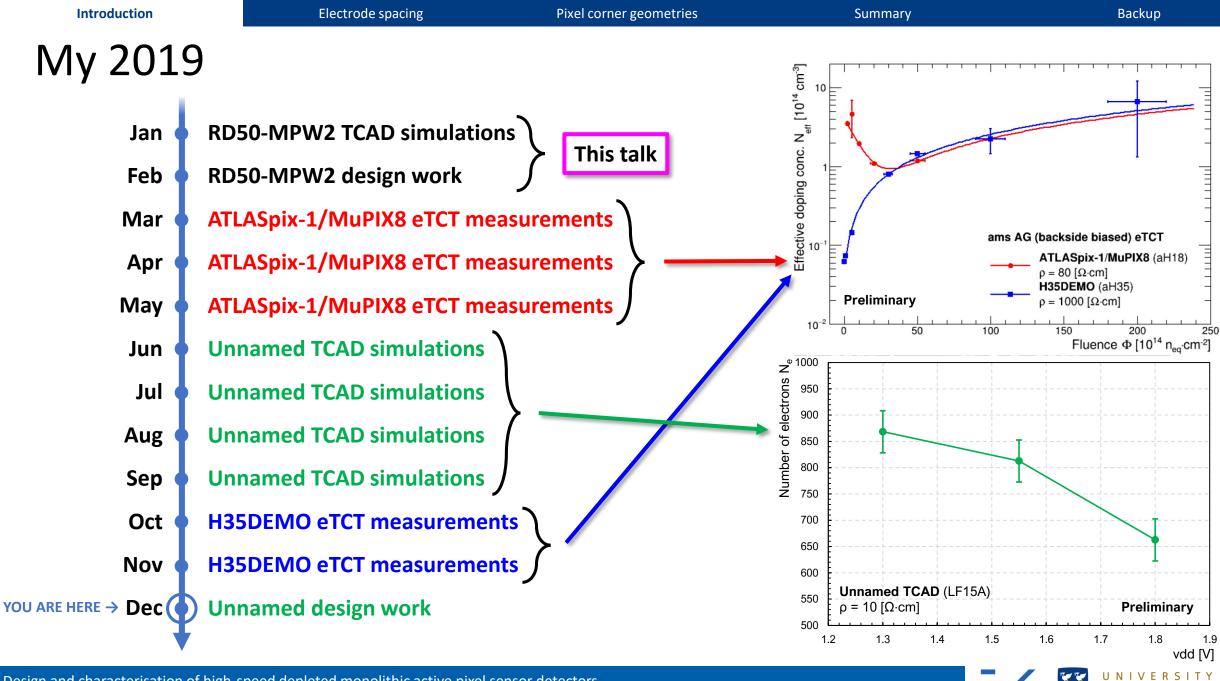

| Introduction | Electrode spacing | Pixel corner geometries | Summary | Backup |

|--------------|-------------------|-------------------------|---------|--------|

| Outling      |                   |                         |         |        |

| Outline      |                   |                         |         |        |

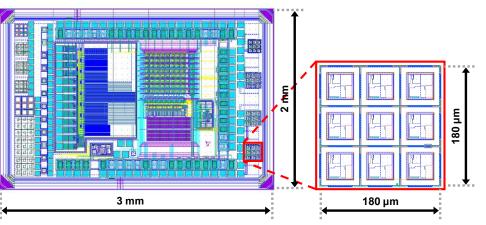

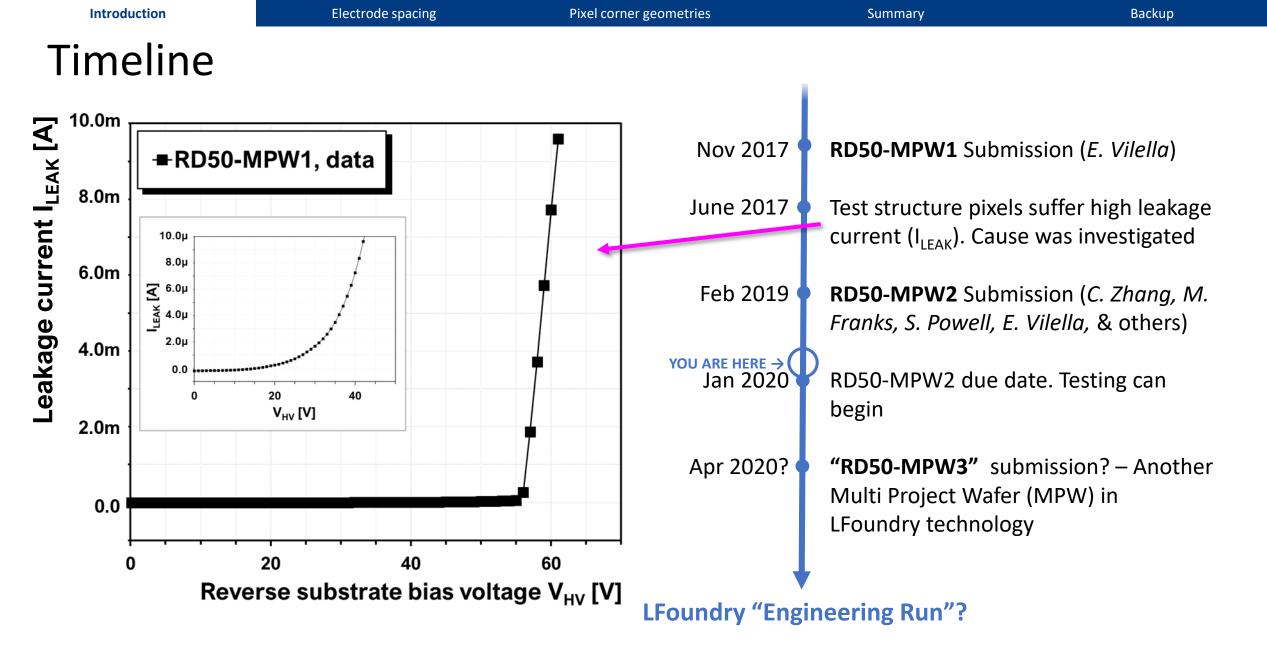

- Timelines

- RD50-MPW1 measurements

- RD50-MPW2 submission

- Breakdown voltage (V<sub>BD</sub>) simulations Sensing diode electrode spacing

- Pixel corner geometries

Summary

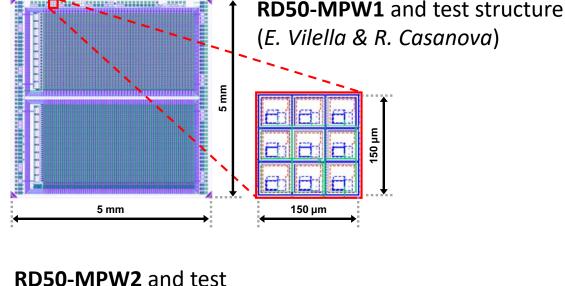

structure (*C. Zhang*, et al.)

Design and characterisation of high-speed depleted monolithic active pixel sensor detectors

0 F

FONDAZIONE BRUNO KESSLER

Design and characterisation of high-speed depleted monolithic active pixel sensor detectors

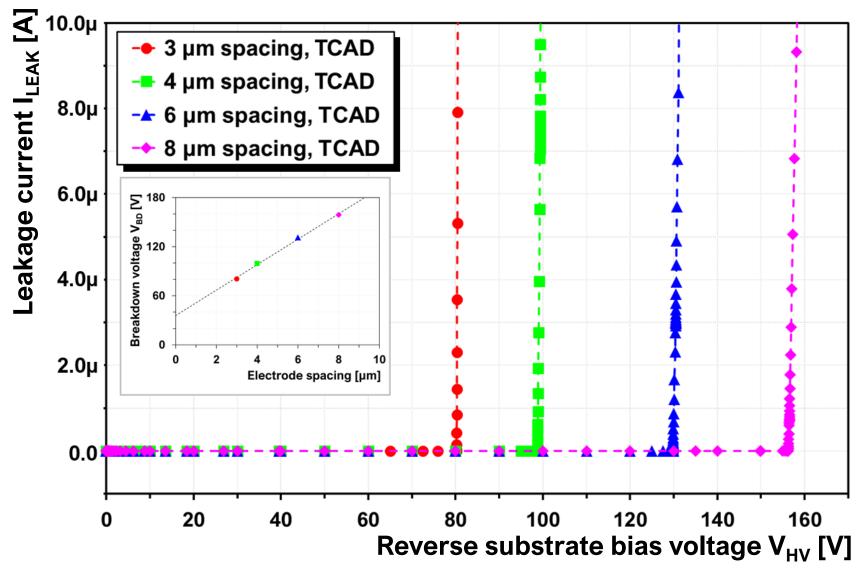

Pixel corner geometries

### **RD50-MPW2** my contributions

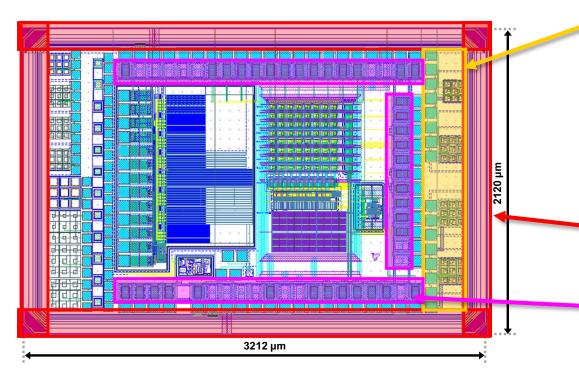

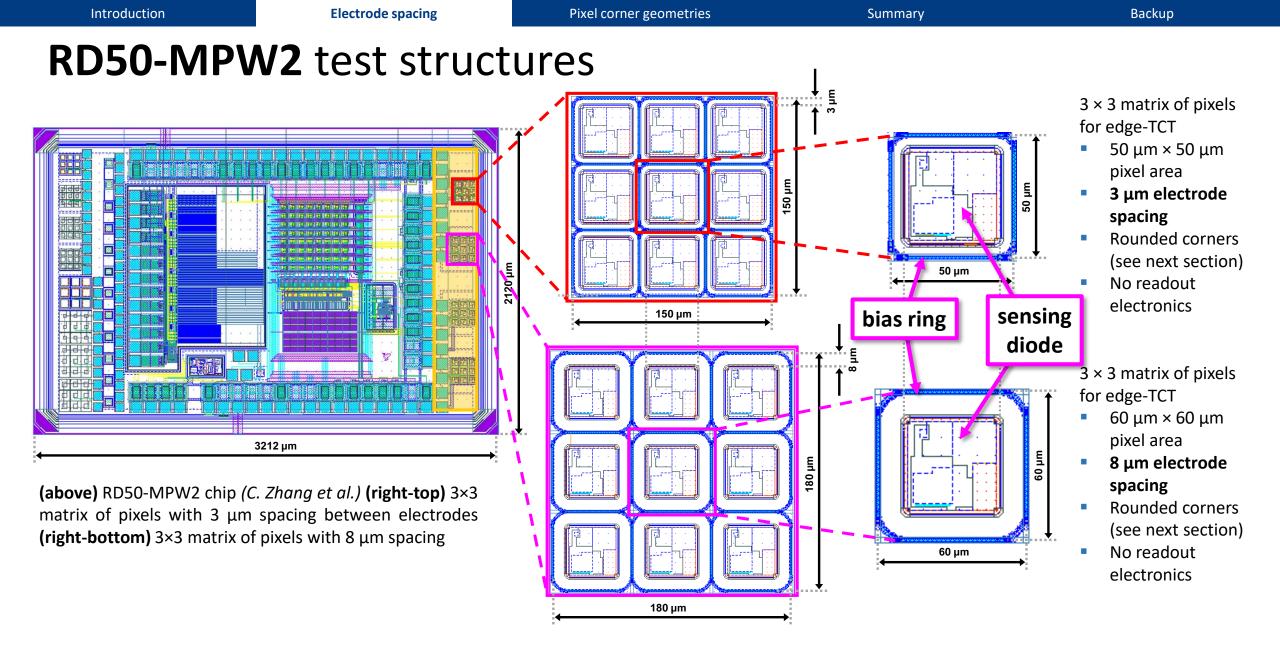

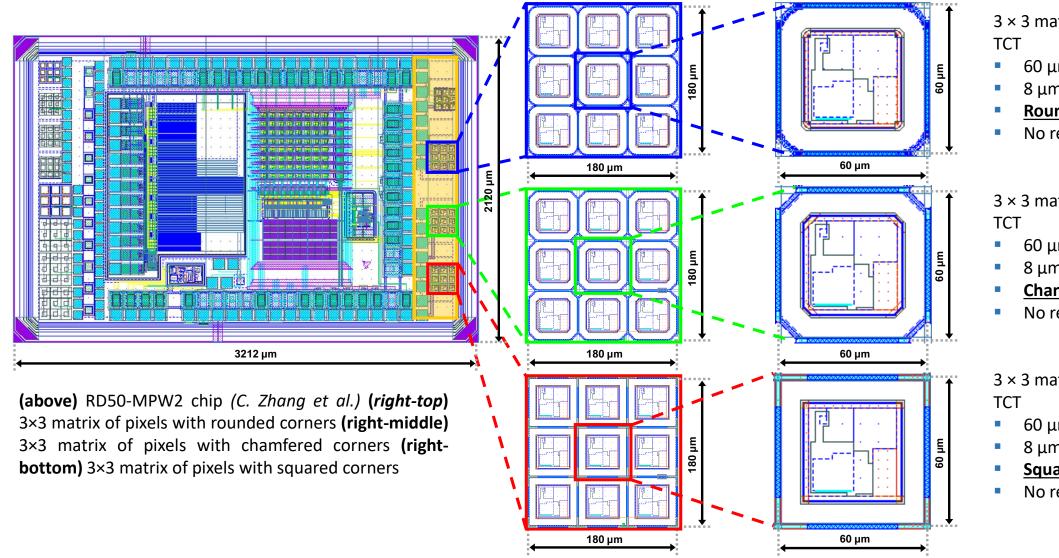

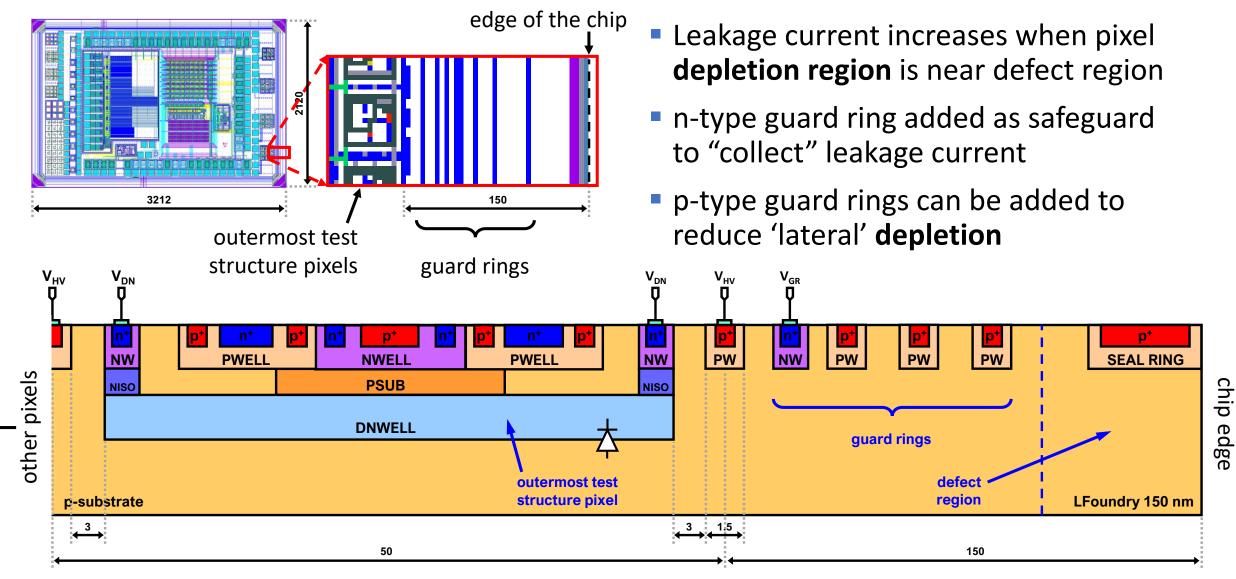

(above) RD50-MPW2 chip (*C. Zhang et al.*) Highlighted areas show my contributions (red) Guard rings included around the edge of the chip (yellow) Test structures for edge-TCT measurements (pink) Modified standard library pad diodes and analog buffers

- Four test structures for e-TCT and I-V measurements

- 3μm rounded corners

- 8µm rounded corners

- 8µm chamfered corners

- 8µm square corners

- Included guard rings at the edge of the device

- Improve leakage current problem

- Modified standard library pad diodes and analog buffers

- Chamfered corners to improve breakdown voltage

- Careful placement of "blocking layers" to improve leakage current

Pixel corner geometries

Backup

### **RD50-MPW2** my contributions

(above) RD50-MPW2 chip (*C. Zhang et al.*) Highlighted areas show my contributions (red) Guard rings included around the edge of the chip (yellow) Test structures for edge-TCT measurements (pink) Modified standard library pad diodes and analog buffers

### Four test structures for e-TCT and I-V measurements

- 3µm rounded corners

- 8µm rounded corners

- 8µm chamfered corners

- 8µm square corners

- Included guard rings at the edge of the device

Improve leakage current problem

- Modified standard library pad diodes and analog buffers

- Chamfered corners to improve breakdown voltage

- Careful placement of "blocking layers" to improve leakage current

Design and characterisation of high-speed depleted monolithic active pixel sensor detectors

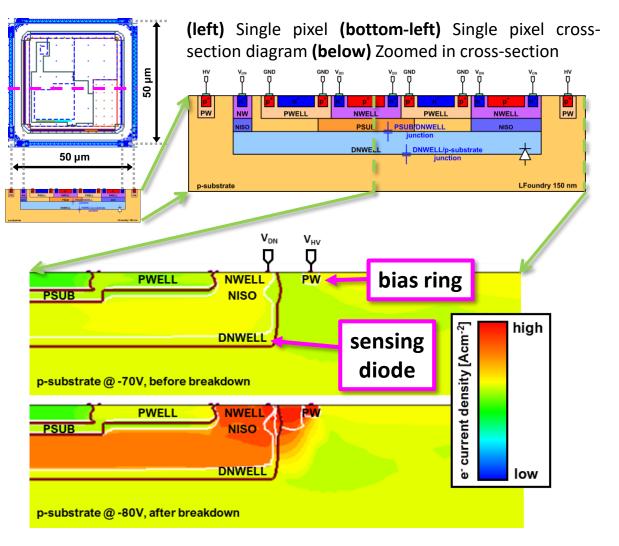

### **RD50-MPW1** breakdown voltage (V<sub>BD</sub>) simulations

Backup

### Backup

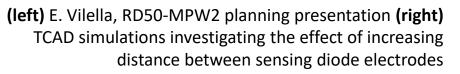

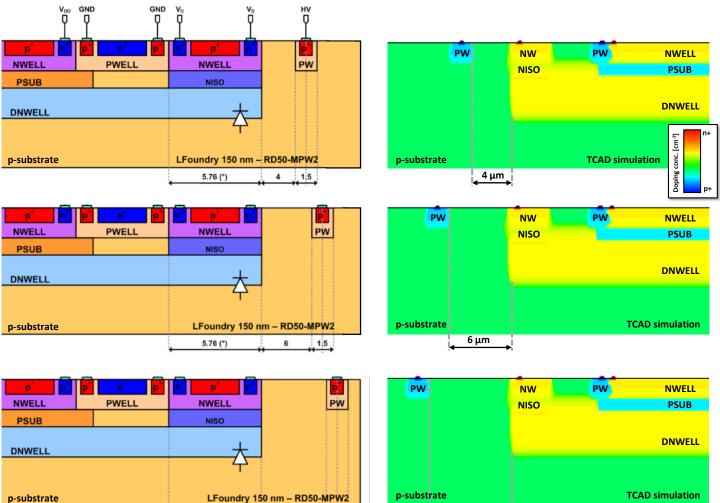

# **RD50-MPW2** breakdown voltage (V<sub>BD</sub>) simulations

- Spacing between electrodes was increased from 3 µm (in RD50-MPW1) to:

- **-** 4 μm

- 🛛 6 μm

- **ο** 8 μm (in **RD50-MPW2**)

- Same breakdown simulations were performed to compare with 3 µm spacing

1.5

5.76 (\*)

8 µm

### **RD50-MPW2** breakdown voltage (V<sub>BD</sub>) simulations

Design and characterisation of high-speed depleted monolithic active pixel sensor detectors

Backup

Electrode spacing

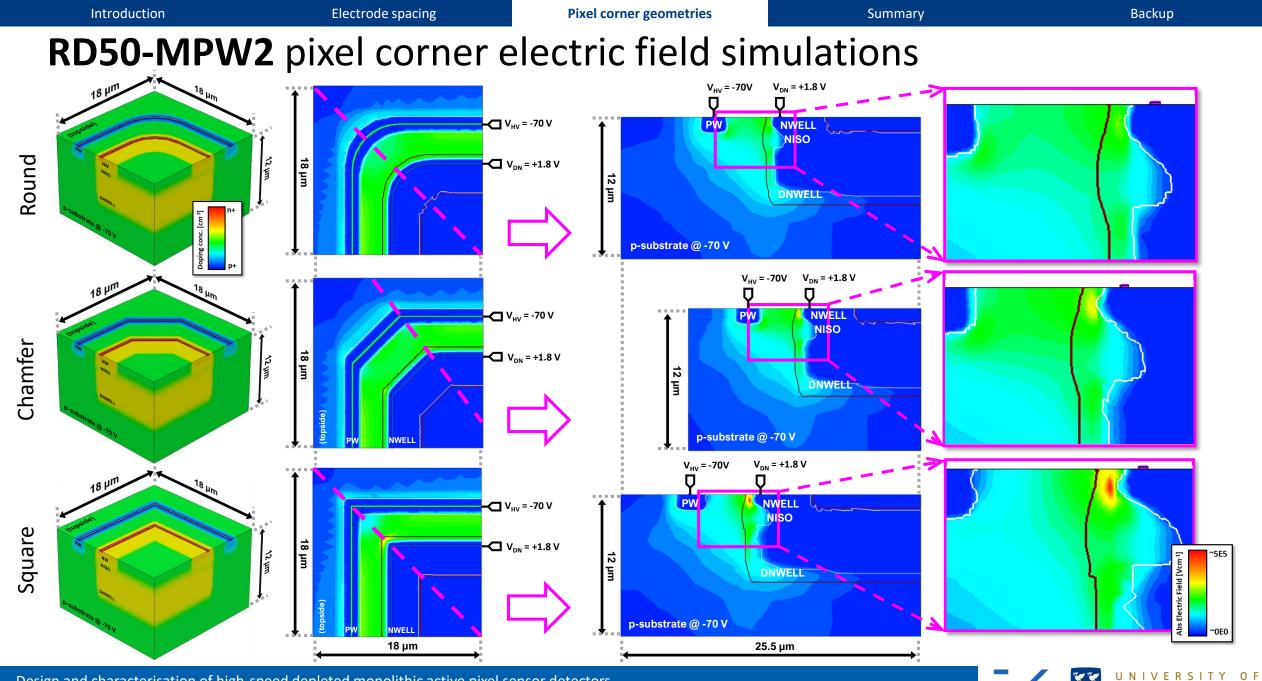

**Pixel corner geometries**

Backup

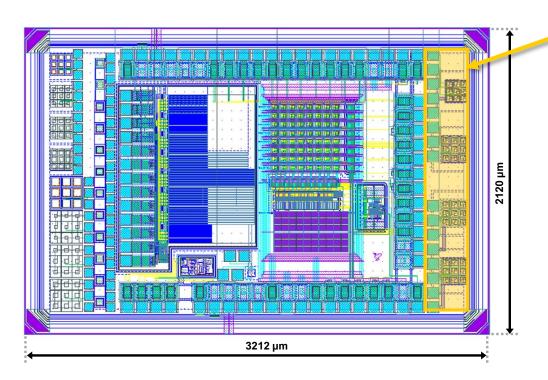

### RD50-MPW2 test structures

3 × 3 matrix of pixels for edge-TCT

- 60  $\mu$ m × 60  $\mu$ m pixel area

- 8 μm electrode spacing

- Rounded corners

- No readout electronics

3 × 3 matrix of pixels for edge-TCT

- 60 μm × 60 μm pixel area

- 8 μm electrode spacing

- Chamfered corners

- No readout electronics

$3 \times 3$  matrix of pixels for edge-TCT

- 60 μm × 60 μm pixel area

- 8 μm electrode spacing

- Squared corners

- No readout electronics

ERPC

FONDAZIONE BRUNO KESSLEE

Design and characterisation of high-speed depleted monolithic active pixel sensor detectors

### Backup

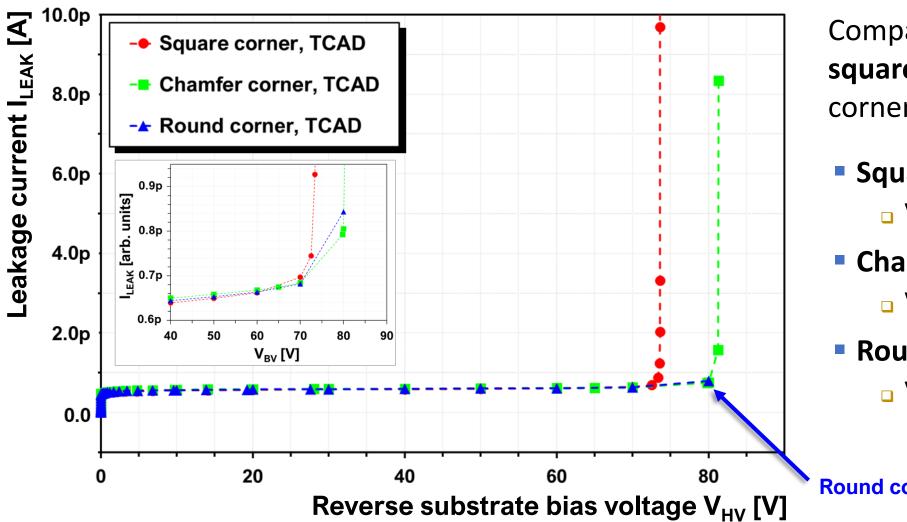

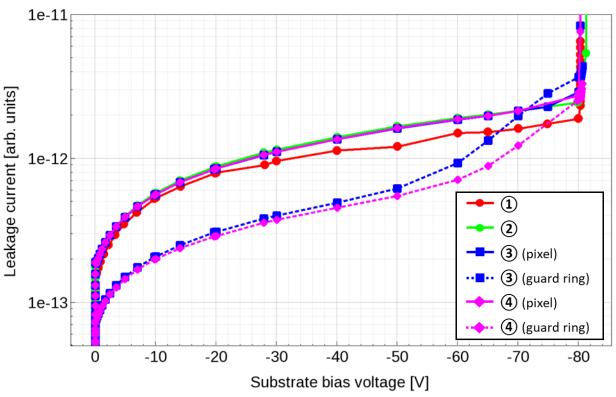

## **RD50-MPW2** V<sub>BD</sub> simulations I-V curves

Comparison of I-V curve of **square**, **chamfer**, and **round** corners:

- Square corners:

□ V<sub>BD</sub> ≈ -70V

- Chamfer corners:

□ V<sub>BD</sub> ≈ -80V

- Round corners:

$\Box$  V<sub>BD</sub>  $\approx$  -80V

**Round corners simulation ended abruptly**

### Summary

- Aims

- Improve leakage current for RD50-MPW2 submission

- Improve breakdown voltage for RD50-MPW2 submission

- RD50-MPW2 submitted Feb 2019

- TCAD simulations of electrode spacing showed increase in breakdown voltage

- TCAD simulations of corner geometries show increase in breakdown voltage

- RD50-MPW2 due to be shipped Jan 2020

- Testing can begin

# Backup slides

HEP Annual Meeting Thursday, 19<sup>th</sup> December 2019

Design and characterisation of high-speed depleted monolithic active pixel sensor detectors

Matthew Franks – HEP Annual Meeting – 19th December 2019 – Slide 16

Backup

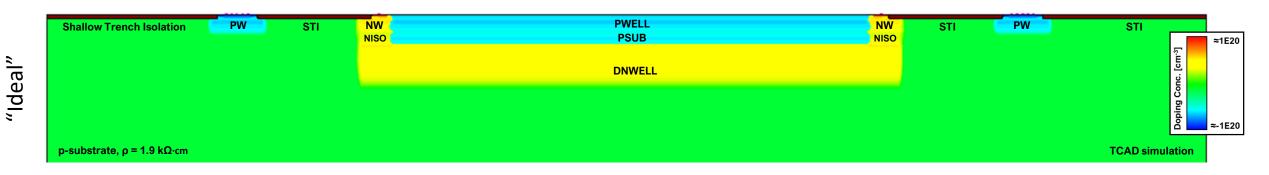

≈1E20

≈-1E20

nc. [cm õ Doping

lation

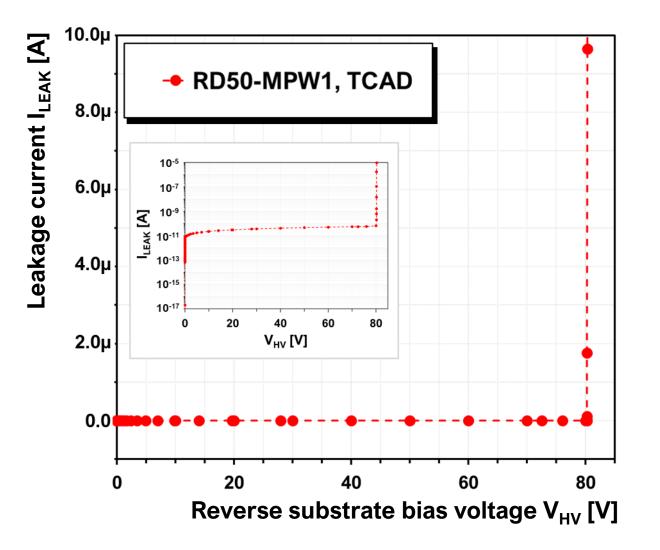

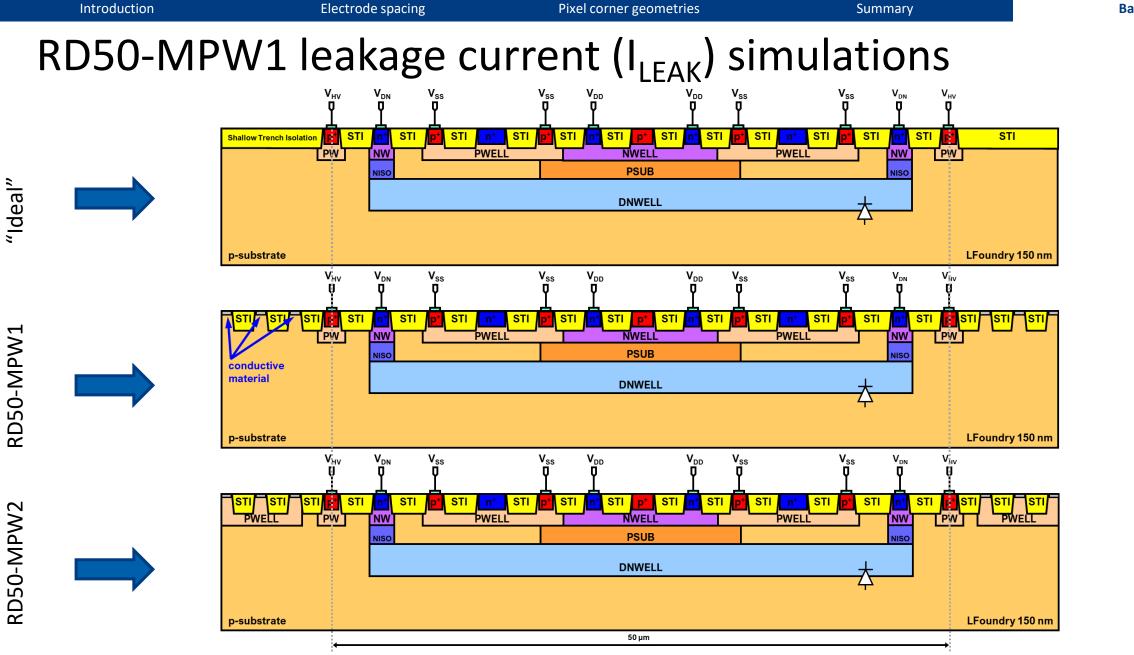

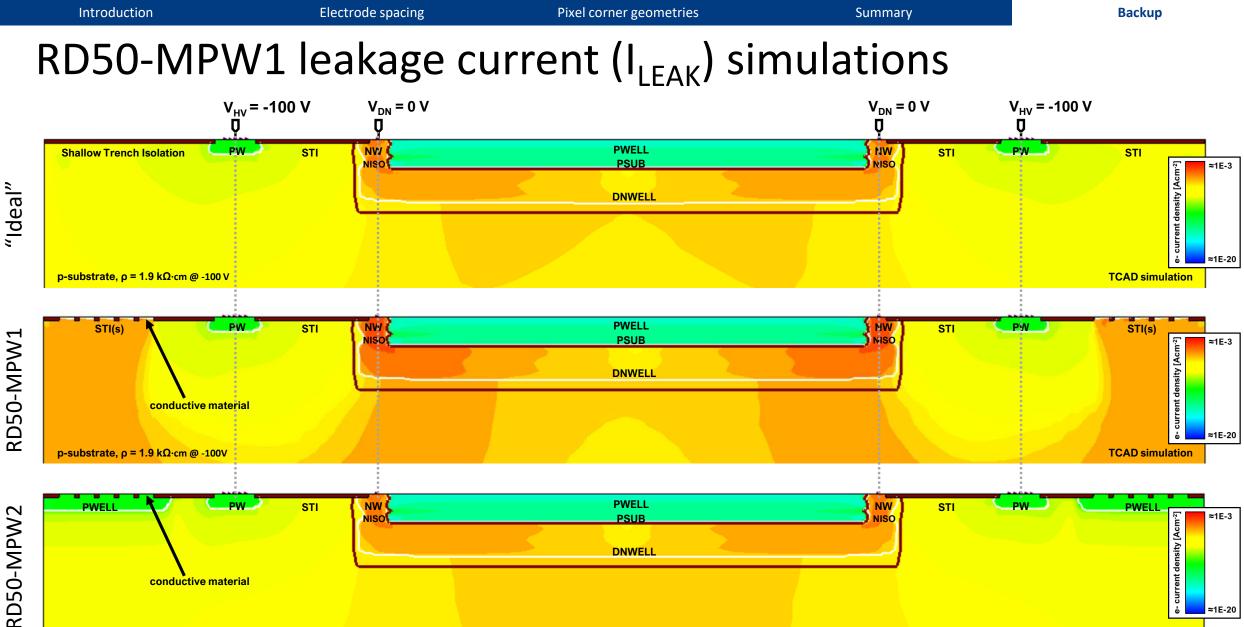

## RD50-MPW1 leakage current (I<sub>LEAK</sub>) simulations

| <b>V1</b> | PW STI                     | NW PWELL<br>NISO PSUB | STI PW | STI(s)           |

|-----------|----------------------------|-----------------------|--------|------------------|

| MP        | STI                        | DNWELL                |        |                  |

| 50-       | conductive material        |                       |        |                  |

| RD        | p-substrate, ρ = 1.9 kΩ⋅cm |                       |        | L<br>TCAD simula |

|          | PWELL PW                    | STI           | NW   | PWELL  | NW   | STI | PW | PWELL           |

|----------|-----------------------------|---------------|------|--------|------|-----|----|-----------------|

| <b>₩</b> |                             | $\rightarrow$ | NISO | PSUB   | NISO |     |    | ≈1E             |

| S        |                             | STI           |      | DNWELL |      |     |    | c. [cm]         |

| P        | conductive material<br>WELL |               |      |        |      |     |    | ping Cor        |

|          |                             |               |      |        |      |     |    | -ā<br>~~1E      |

| p-sut    | ostrate, ρ = 1.9 kΩ·cm      |               |      |        |      |     |    | TCAD simulation |

p-substrate, ρ = 1.9 kΩ·cm @ -100V

Design and characterisation of high-speed depleted monolithic active pixel sensor detectors

**TCAD** simulation

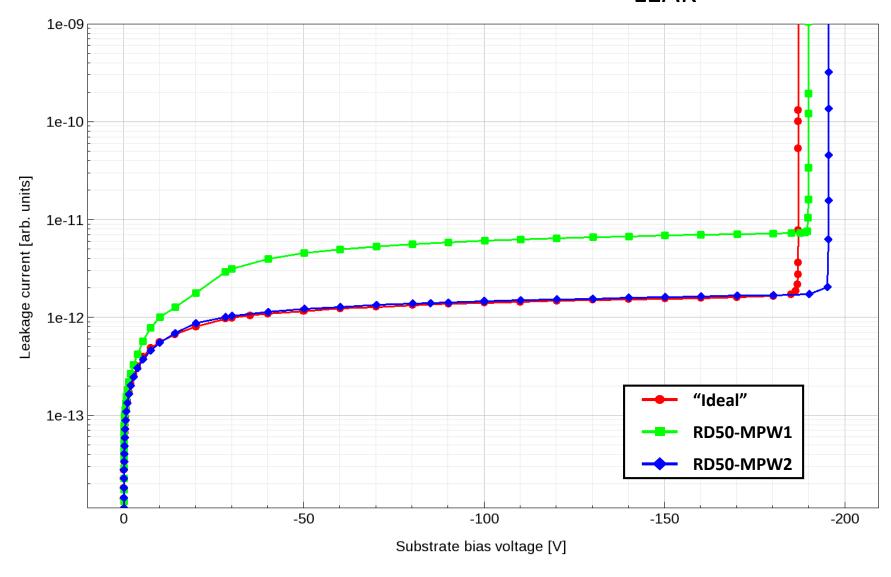

### RD50-MPW1 leakage current (I<sub>LEAK</sub>) simulations

Comparison of I-V curves of the three simulations:

- Increase in I<sub>LEAK</sub> when conductive material is present on the surface (RD50-MPW1)

- I<sub>LEAK</sub> is reduced when conductive material is placed in PWELL (RD50-MPW2)

Design and characterisation of high-speed depleted monolithic active pixel sensor detectors

NIVERSITY

OF

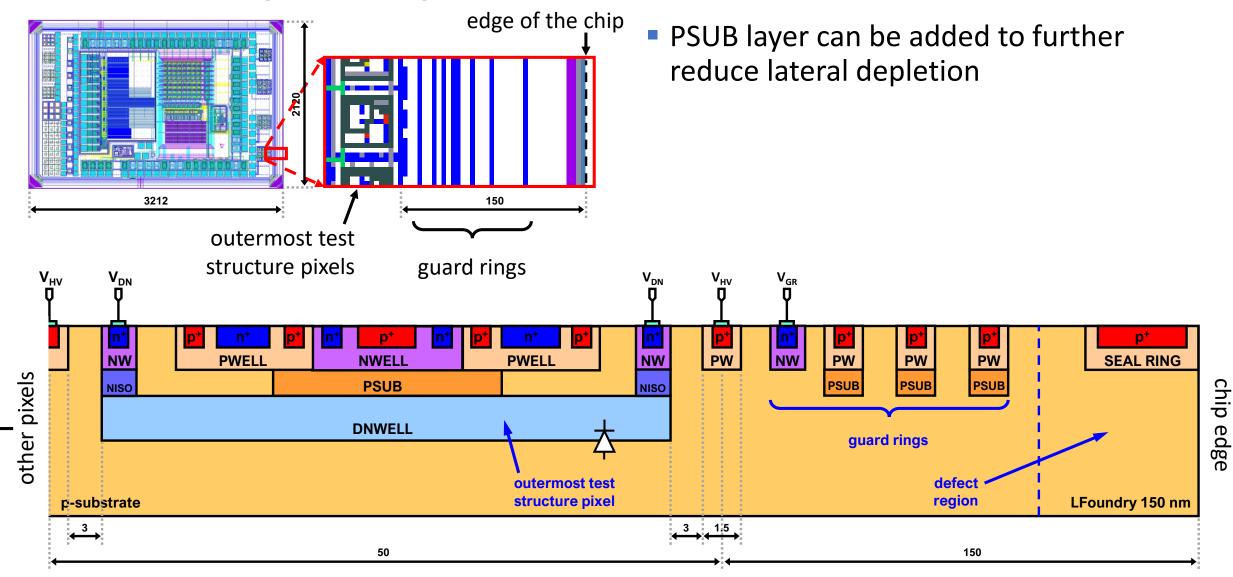

### **RD50-MPW2** guard rings

| Introc | luction |

|--------|---------|

|        |         |

### **RD50-MPW2** guard rings

Design and characterisation of high-speed depleted monolithic active pixel sensor detectors

ΟF

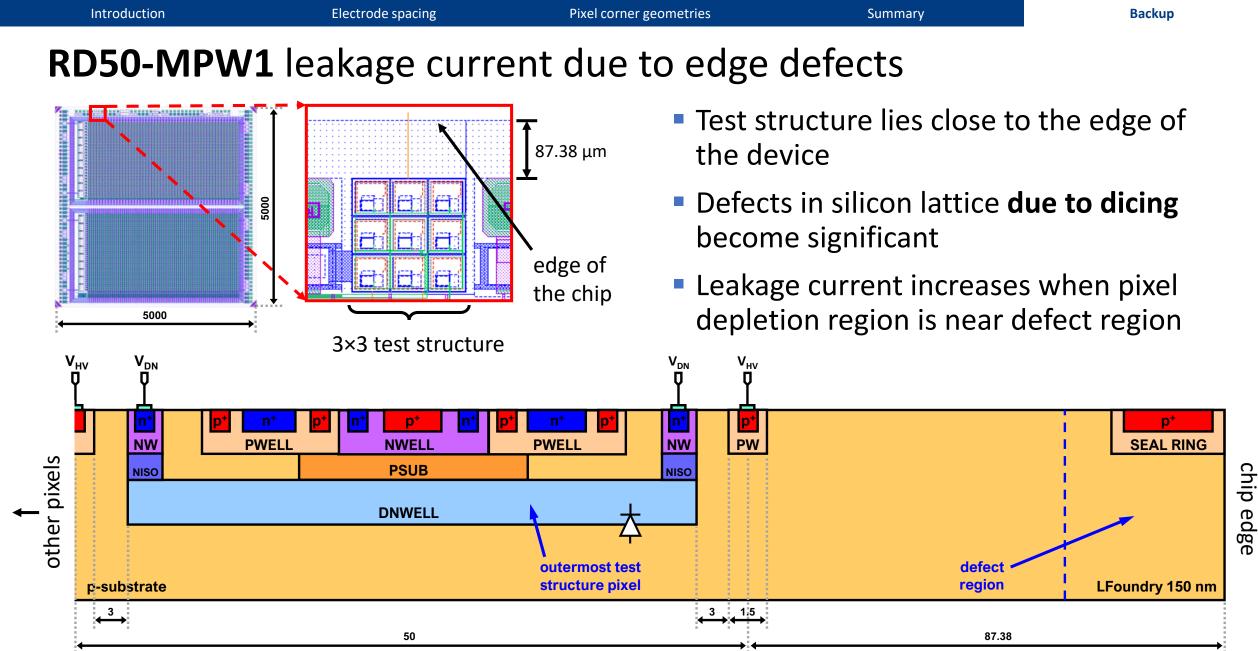

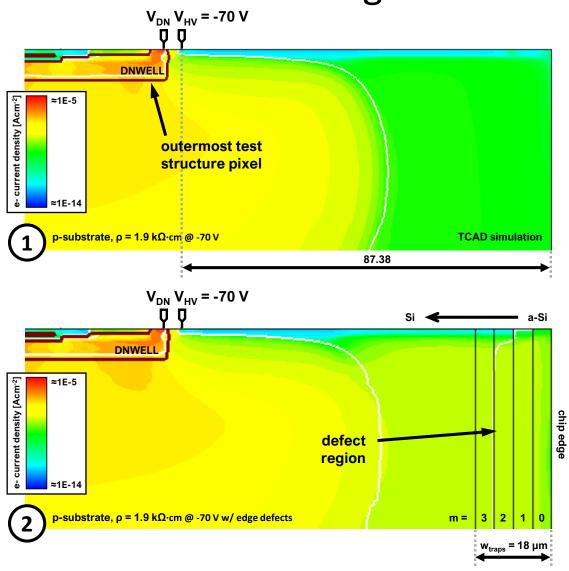

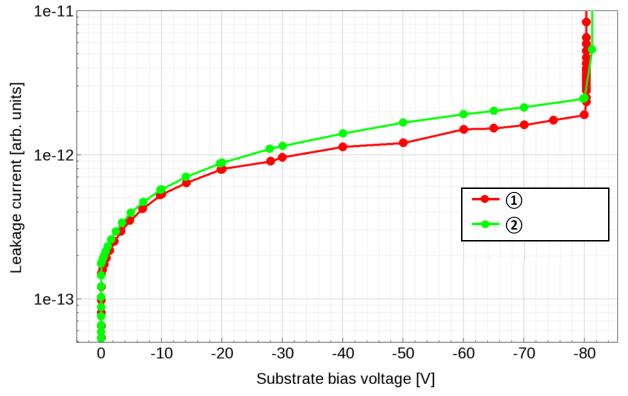

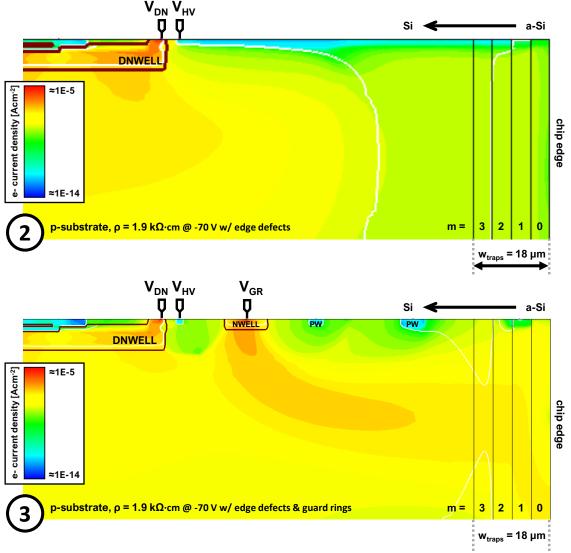

### RD50-MPW1 leakage current due to edge defects

- Two simulations, with and without edge defects (Damage modelled as amorphous silicon (Noschis et al. 2007))

- Simulated I<sub>LEAK</sub> higher when edge defects are present

Matthew Franks – HEP Annual Meeting – 19th December 2019 – Slide 23

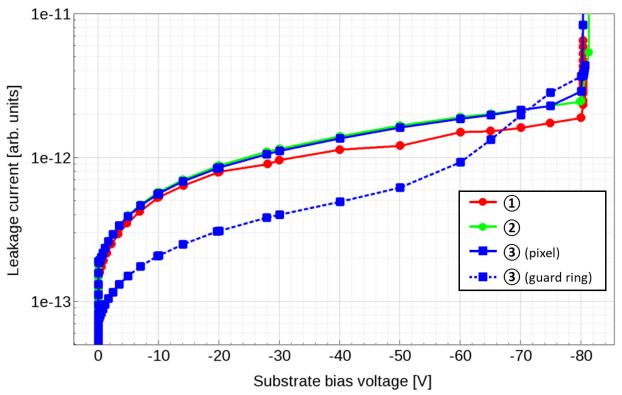

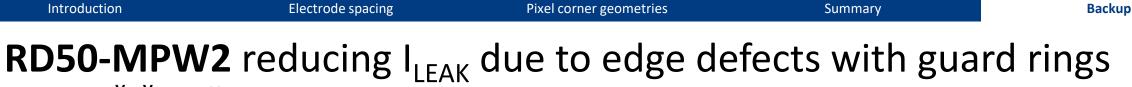

## **RD50-MPW2** reducing $I_{LEAK}$ due to edge defects with guard rings

- Similar I<sub>LEAK</sub> measured at both pixels

- n-type guard ring acts as another diode, increasing lateral depletion into defect region, but collects additional current

Design and characterisation of high-speed depleted monolithic active pixel sensor detectors

Si constrained Si constrained

- Additional deep p-type well PSUB under guard rings reduces lateral depletion

- This reduces simulated I<sub>LEAK</sub> further

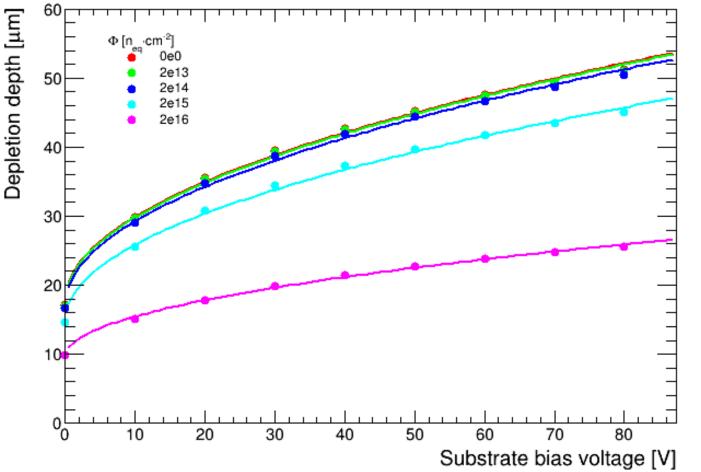

| Introduction | Electrode spacing | Pixel corner geometries | Summary     | Backup |

|--------------|-------------------|-------------------------|-------------|--------|

| RD50-MPW1    | radiation         | damage simula           | tion and an | alvsis |

Using **RD50-MPW1** pixel simulations:

- Simulations have been run for fluences 2E13, 2E14, and 2E15, and 2E16 [n<sub>eq</sub>·cm<sup>-2</sup>]

- Substrate resistivity  $\rho = 500 \Omega \cdot cm$

| Туре     | Energy<br>(eV) | Trap | σ <sub>e</sub> (cm²)   | σ <sub>h</sub> (cm²)   | η<br>(cm <sup>-1</sup> ) |

|----------|----------------|------|------------------------|------------------------|--------------------------|

| Acceptor | Ec-0.42        | VV   | 9.5*10 <sup>-15</sup>  | 9.5*10 <sup>-14</sup>  | 1.613                    |

| Acceptor | Ec-0.46        | VVV  | 5.0*10 <sup>-15</sup>  | 5.0*10 <sup>-14</sup>  | 0.9                      |

| Donor    | Ec+0.36        | CiOi | 3.23*10 <sup>-13</sup> | 3.23*10 <sup>-14</sup> | 0.9                      |

**Table:** (*D. Pennicard, UoGlasgow, PPT*) TCAD simulated "Modified Uni. of Perugia" model charge trapping levels defined within silicon bandgap