# **ANNUAL MEETING**

# **HVCMOS ASIC DESIGN**

28/04/21

- An ideal Bandgap voltage reference generates a DC voltage that is independent of:

- Temperature

- Power Supply

- Process Variations

- A precise voltage reference is need for many applications including:

- A/D and D/A Converters

- LDO Voltage Regulators

- Linear Regulators

| L  | PIXEL Matrix            |                                                                                                                        |

|----|-------------------------|------------------------------------------------------------------------------------------------------------------------|

| П  | Analog Buffer           |                                                                                                                        |

| Ш  | Test Structures         |                                                                                                                        |

| IV | SEU Tollerant<br>Memory |                                                                                                                        |

| V  | Bandgap                 |                                                                                                                        |

|    |                         |                                                                                                                        |

|    |                         |                                                                                                                        |

|    |                         |                                                                                                                        |

|    |                         | RD50-MPW2 Submitted in January 2019                                                                                    |

|    |                         |                                                                                                                        |

|    |                         |                                                                                                                        |

|    |                         | <ul> <li>RD50-MPW2 Submitted in January 2019</li> <li>Chip received from manufacture in Febru</li> <li>2020</li> </ul> |

#### RD50-MPW2 MEASUREMENTS -Bandgap Reference

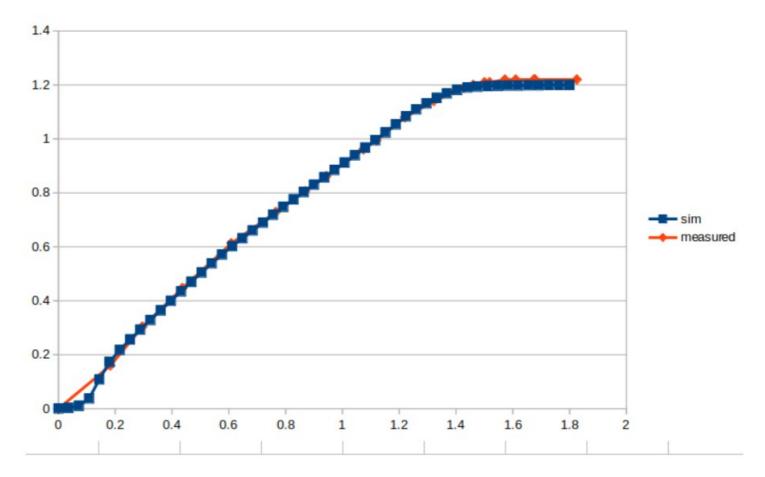

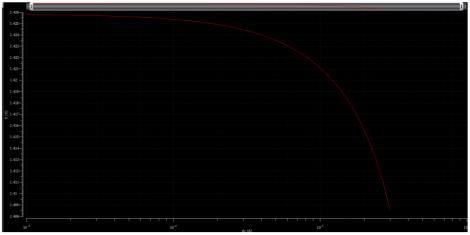

- Measured Results for the bandgap reference circuit designed for RD50-MPW2 show almost perfect agreement with simulated expectation

- Output voltage is extremely stable in the operating range (1.4 to 1.8 V)

- This will allow for bias voltages throughout the chip to be derived from a much more stable source than previous designs

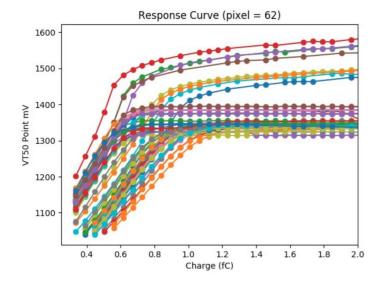

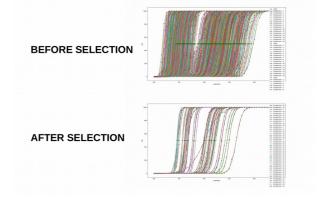

#### RD50-MPW2 ACTIVE PIXEL MATRIX MEASUREMENTS

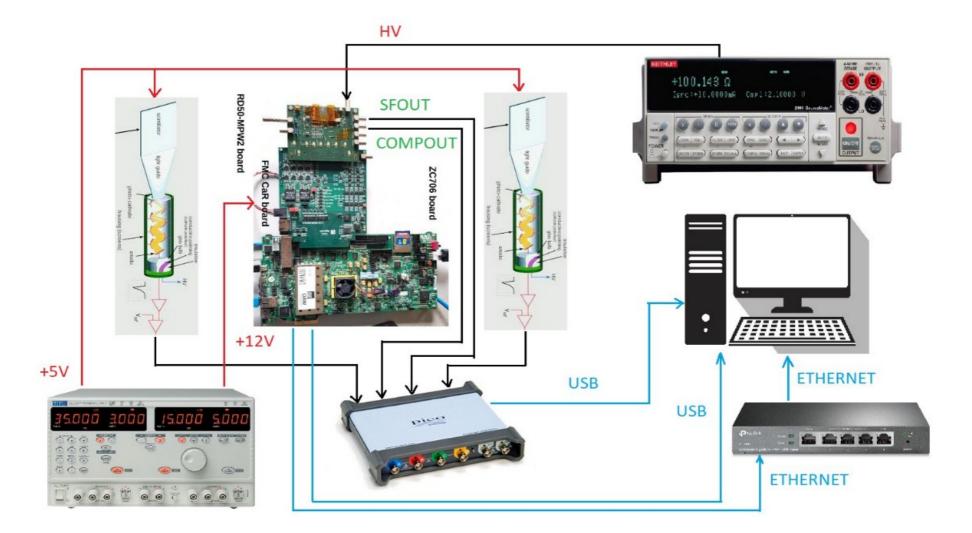

- Software and firmware developed to configure,

- readout and analyse RD50-MPW2

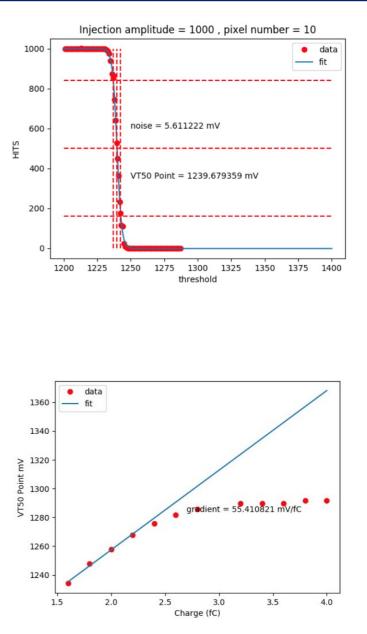

- Measurements including S-curves, Response Curves

- DAC trimming, Gain calculations and pixel to pixel gain

injected charge

- and noise distributions

- MPW2 has now

vt50

linear

- been very well

- characterised

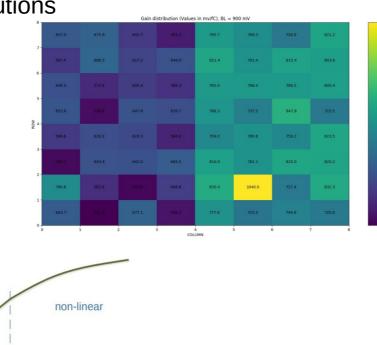

Plotting the VT50 point of these S-curves as a function of injection amplitude gives us the gain of the pixel

~4fC

## **RD50-MPW2 MEASUREMENTS**

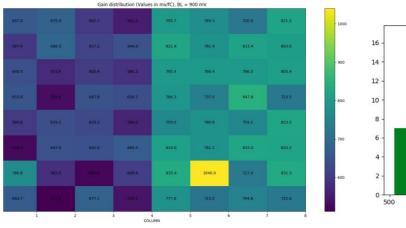

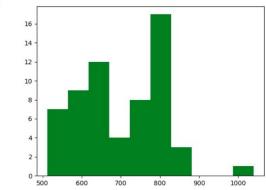

- Gain distribution shows 2 distinct patterns of gain values

- This is expected as the matrix contains 2 flavours of pixel (switched reset and continuous) split between the right and left sides of the matrix

- The 2 different gains can be seen represented as the gradients of the response curves (top left), the colour difference in the 2d Gain map of the matrix (middle) or the 2 peaks of the gain histogram (top right)

### **RD50-MPW2 TESTBEAM**

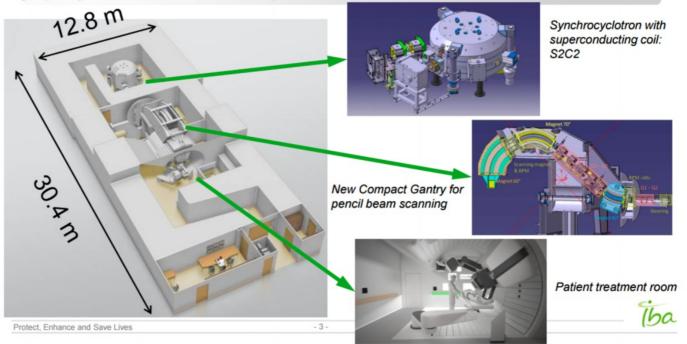

**IBA Proteus One** – S2C2 synchrocyclotron characteristics

Protons delivered in bunches with a 1 kHz reputation rate

- Bunch length: 10us

- Min. Protons/s: 107

- Min. Protons/bunch: 10<sup>5</sup>

- Beam energies from 70-229 MeV

- Min beam spot size: 3.5mm radius

- Gantry angles from 0 270deg

With thanks to F. Risser (IBA)

#### The New IBA Single Room Proton Therapy Solution: ProteusONE®

High quality PBS cancer treatment: compact and affordable

#### **RD50-MPW2 TESTBEAM**

## **RD50-MPW2 BEAM TELESCOPE**

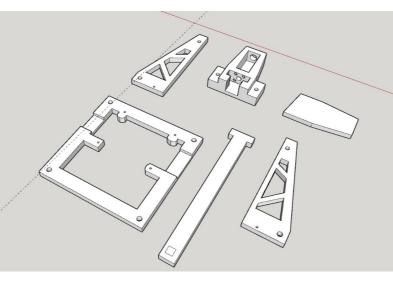

The testbeam telescope has been designed to be 3d printed to allow the design to be modified easily

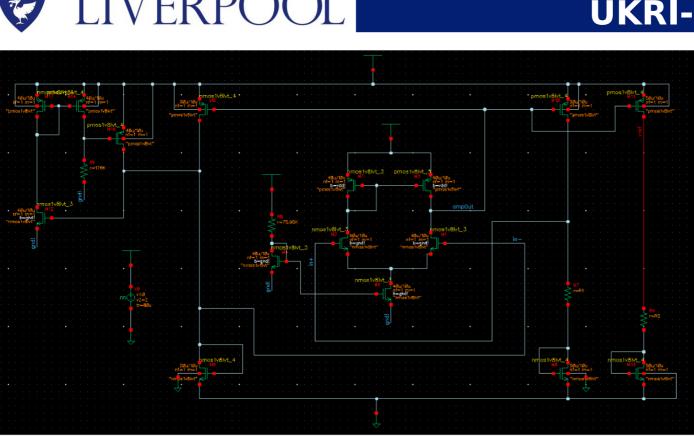

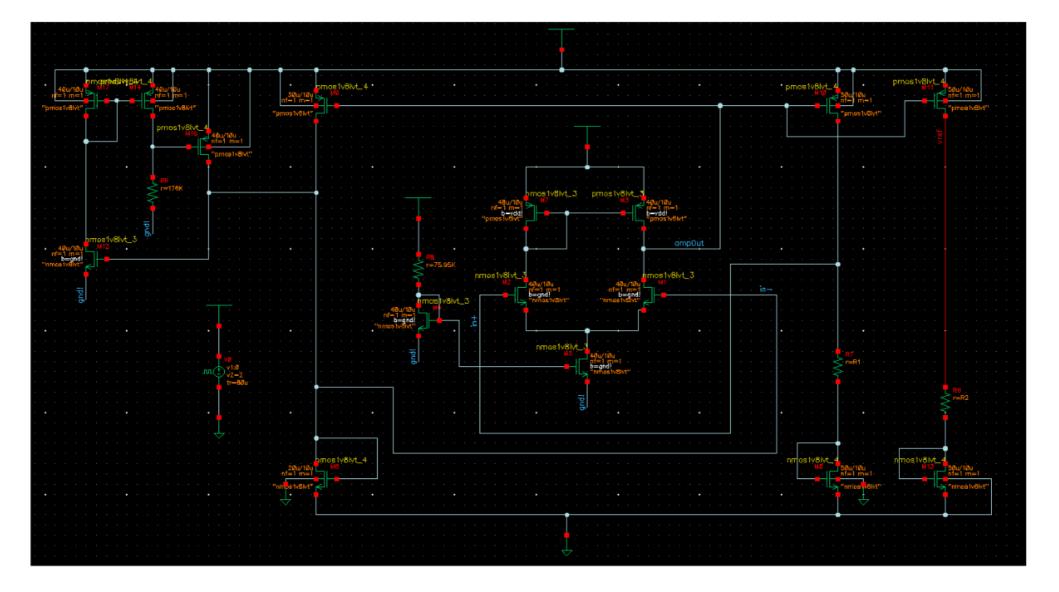

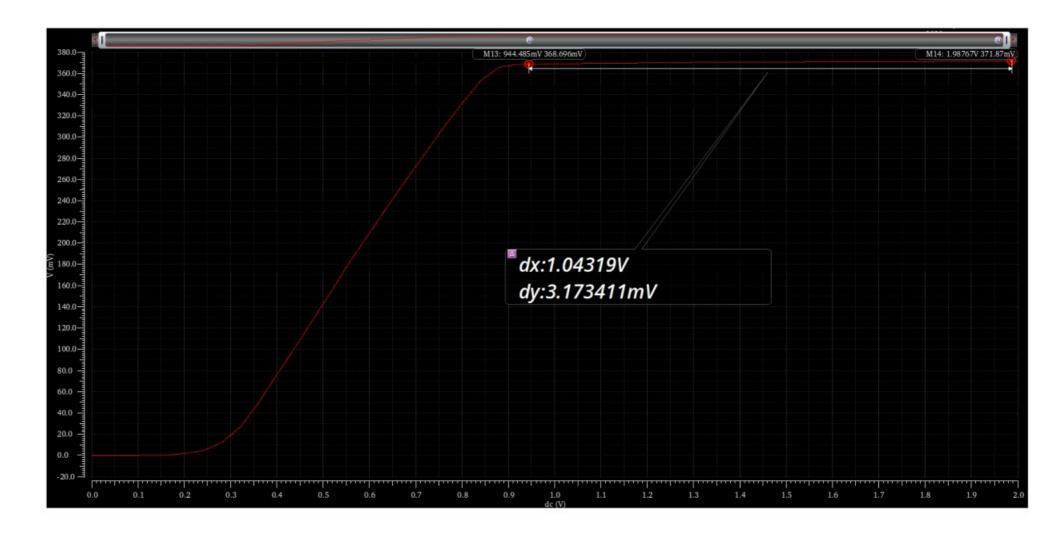

#### FULLY CMOS BASED BANDGAP UKRI-MPW0

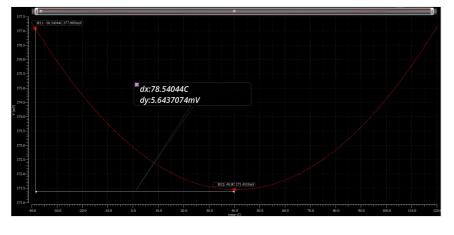

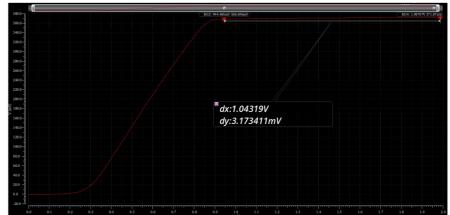

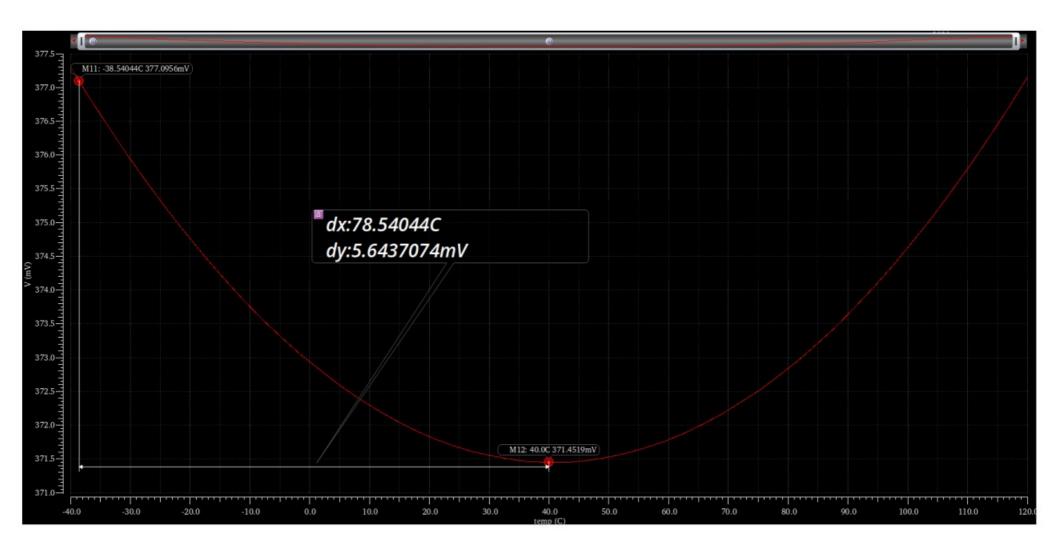

- Simulations of fully CMOS based bandgap for UKRI-MPW0 show

- Output voltage changes by 3.17mV over the entire operating range (0.8-1.8V)

- Output voltage changes by 5.6mV for a change in ambient temperature from -40 to +120 degrees Celcius

#### UNIVERSITY OF LIVERPOOL

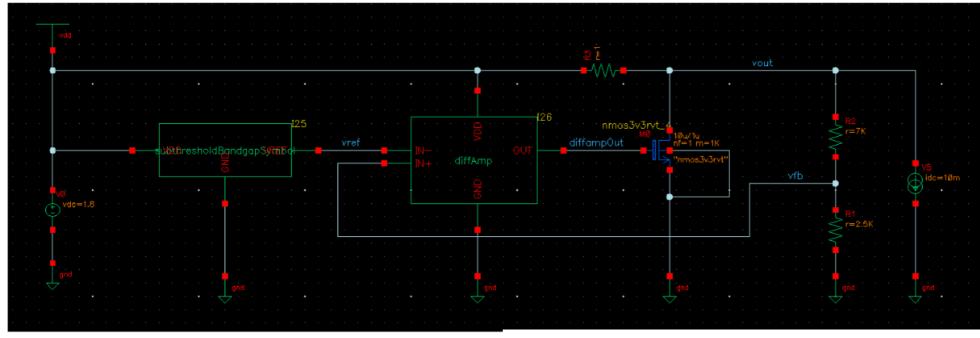

## SHUNT REGULATOR UKRI-MPW0

- A Shunt regulator has also been designed

- for UKRI-MPW0 building on the success of the bandgap in RD50-MPW2

- A regulator provides not only a stable voltage, but the capability to provide significant current

- This allows power supplies to be generted on chip reducing the need for external compenents and PCB area – reducing the material budget

Fully mosfet regulator set for arbitrary 1.4V ouput

Ouput voltage changes by less than 5mV for a current draw from 0 to 100mA

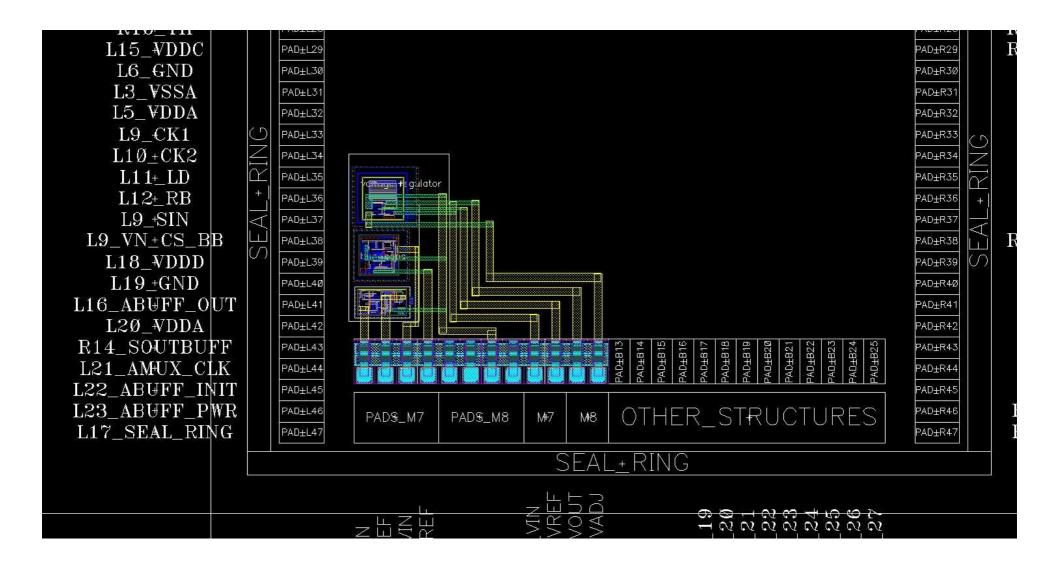

#### PLACED AND ROUTED BLOCKS UKRI-MPW0

#### SUMMARY

- CHIPS SUBMITTED

- RD50-MPW1

- RD50-MPW2 (Designed BJT bandgap reference)

- UKRI-MPW0 (Designed BJT bandgap reference , Fully CMOS bandgap reference and Shunt regulator)

- Chips characterised

- RD50-MPW1 gain, noise, thresholds

- RD50-MPW2 gain, noise, thresholds (Testbeam planned for 10th May)

- Awaiting Delivery

- UKRI-MPW0

- Further work

- Submit design for readout PCB for UKRI-MPW0

- Write FPGA firmware for UKRI-MPW0 DAQ in VHDL and C

- Write FPGA firmware for decode addresses for UKRI-MPW0 DAQ in VHDL

- Write GUI to configure UKRI-MPW0 in C++

- Confirm measurements of RD50-MPW2 with testbeam

- Characterise UKRI-MPW0

# BACKUP SLIDES FOLLOW

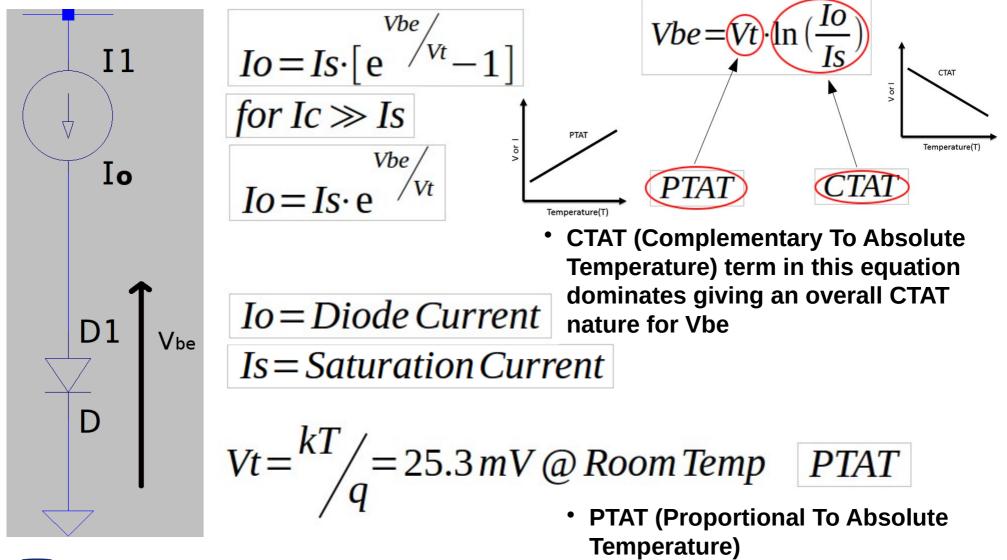

#### UNIVERSITY OF LIVERPOOL Design Principles

**RD50**

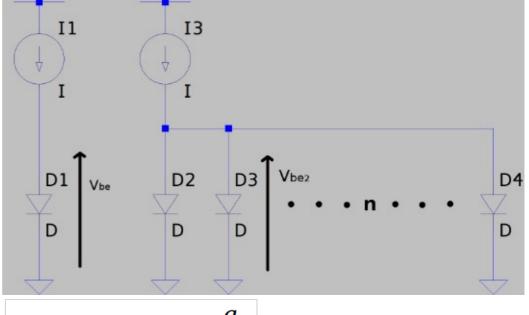

### **UNIVERSITY OF LIVERPOOL** How to generate a PTAT

• If we can cancel out this term we generate a pure PTAT

$$Vbe = Vt \cdot \ln\left(\frac{Io}{Is}\right)$$

$Vbe_2 = Vt \cdot \ln\left(\frac{Io}{Is}\right)$

$$Vbe - Vbe_2 = Vt \left[ \ln\left(\frac{Io}{Is}\right) - \ln\left(\frac{Io}{n \cdot Is}\right) \right] \quad \ln(a) - \ln(b) = \ln\left(\frac{a}{b}\right)$$

$$Vbe - Vbe_2 = Vt \cdot \ln\left[\left(\frac{Io \cdot n \cdot Is}{Io \cdot Is}\right)\right]$$

$$Vbe - Vbe_2 = Vt \cdot \ln(n)$$

$PTAT$

• Note. These equations rely on both current sources being equal. To achieve this a current mirror circuit is required

PTAT

Temperature(T)

V or

**RD50**

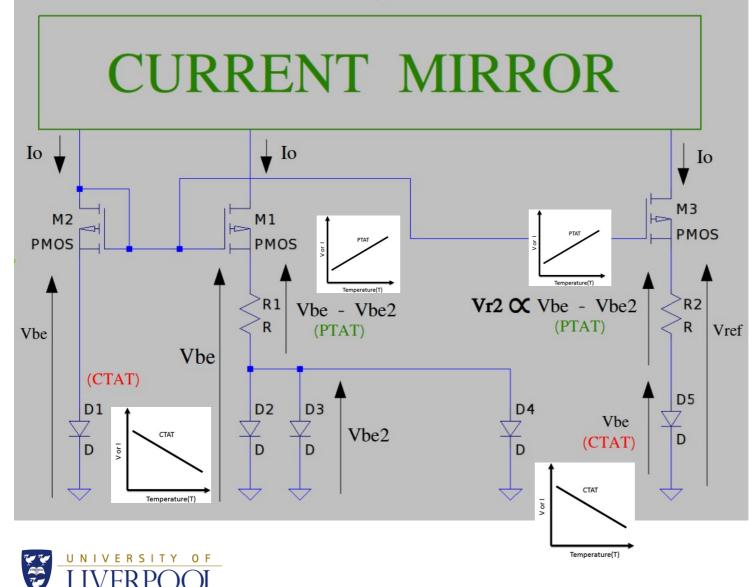

#### O F **Bandgap Design Principles** H

FRP

**RD50**

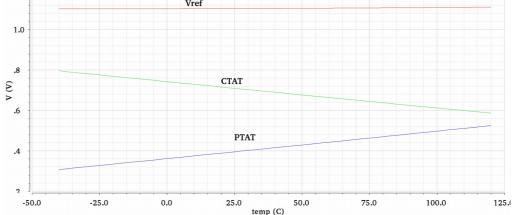

- Vref is a combination of • both a PTAT and a CTAT term

- By controlling the ratio of ٠ resistor values R1/R2 and the number of diodes n we can cancel out the PTAT and CTAT terms giving an output that is independent of Temperature

ERS

LIVERPO

0 F

#### FULLY CMOS BASED BANDGAP UKRI-MPW0

# LIVERSITY OF

#### FULLY CMOS BASED BANDGAP UKRI-MPW0

#### FULLY CMOS BASED BANDGAP UKRI-MPW0

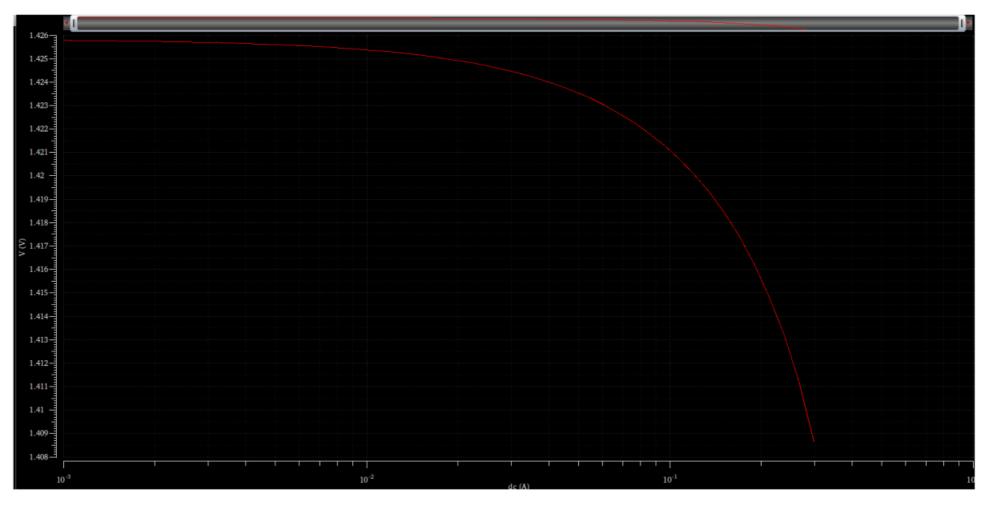

#### LIVERSITY OF SHUNT REGULATOR PERFORMANCE

- Fully mosfet regulator set for arbitrary 1.4V ouput

- Ouput voltage changes by less than 5mV for a current draw from 0 to 100mA