## **R&D of HV–CMOS detectors** 2021 HEP Annual Meeting, 19–20 May 2022

Chenfan Zhang on behalf of the HV-CMOS group

### **HV-CMOS: Monolithic Pixel Detectors**

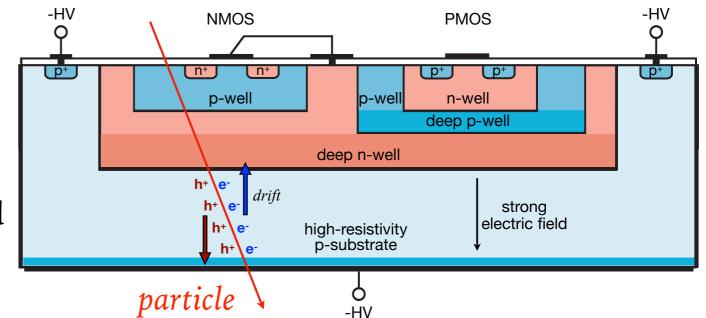

- Monolithic: Sensor and readout electronics in a single silicon wafer.

- Single layer structure: low material thickness (50 μm);

- No bump-bonding: Small pixel size (< 50 μm × 50 μm); reduced production cost (~ £100k/m<sup>2</sup>);

- High bias voltage: fast charge collection by drift (~ 200 ps) and high radiation tolerance (5×10<sup>15</sup> 1 MeV n<sub>eq</sub>/cm<sup>2</sup>).

- The Mu3e experiment has chosen HV-CMOS pixel detectors and many others are considering them: LHCb, proton EDM, PANDA. And applications fields other than HEP experiments.

#### **Our Collaborations**

- **CERN-RD50** collaboration focuses on developing radiation-tolerant detectors.

- Liverpool has the leadership of its CMOS Working Group, we do:

- ► ASIC design

- ► TCAD simulations

- DAQ development

- Chip performance evaluation

- Currently involves 17 institutes across the world:

- Development goals:

- ► High radiation tolerance (low leakage and high breakdown)

- excellent time resolution and pixel granularity

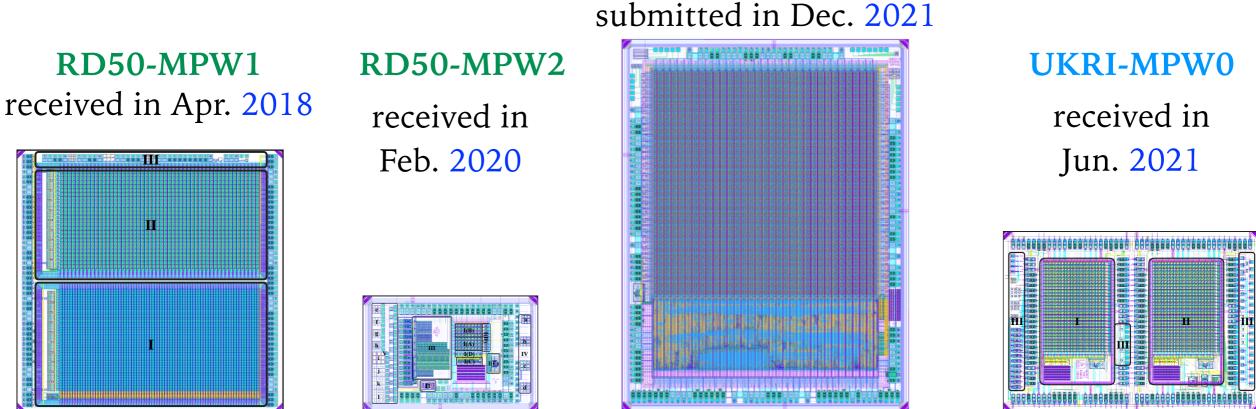

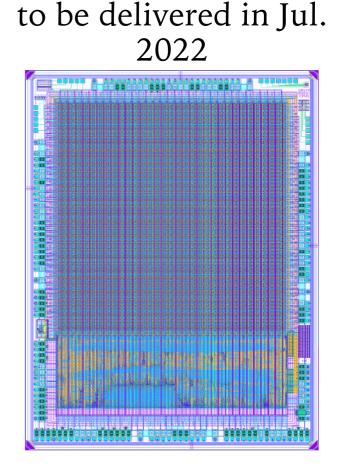

RD50-MPW3

- **RD50-MPW1**: test the LF150 process, low  $V_{BD}$  (55 V) and high  $I_{Leak}$  (~  $\mu$ A).

- **RD50-MPW2**: high  $V_{BD}$  (130 V), low  $I_{Leak}$  (~ nA) and fast analog pixel.

- **RD50-MPW3**: implements large pixel matrices with advanced digital readout.

- UKRI-MPWO: first backside-only biased, high  $V_{BD}$  (> 600 V).

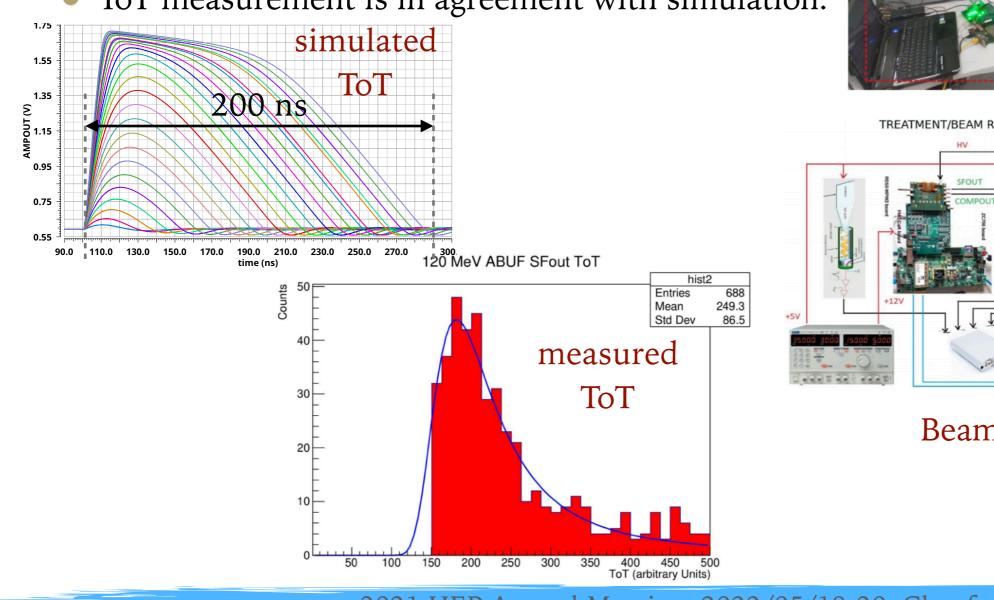

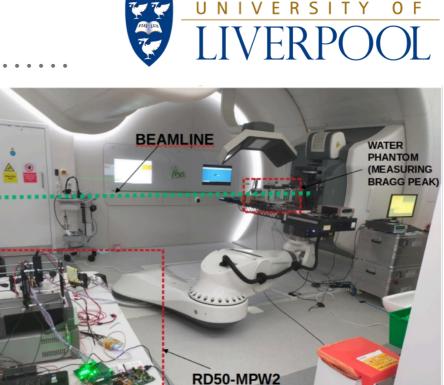

#### Beam test of RD50-MPW2

- First beam test by Liverpool HV-CMOS group.

- Characterise RD50-MPW2 at Rutherford Cancer Centre in Northumberland in May 2021.

- Protons delivered in bunches with a 1 kHz rate

- ► Beam energy: 70 -229 MeV

- ToT measurement is in agreement with simulation.

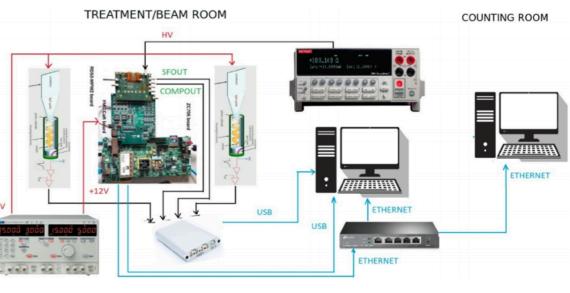

TELESCOPE AND DAØ

Beam test DAQ setup

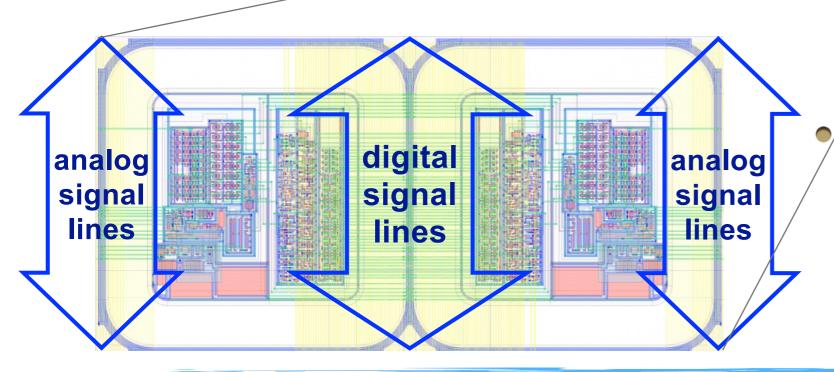

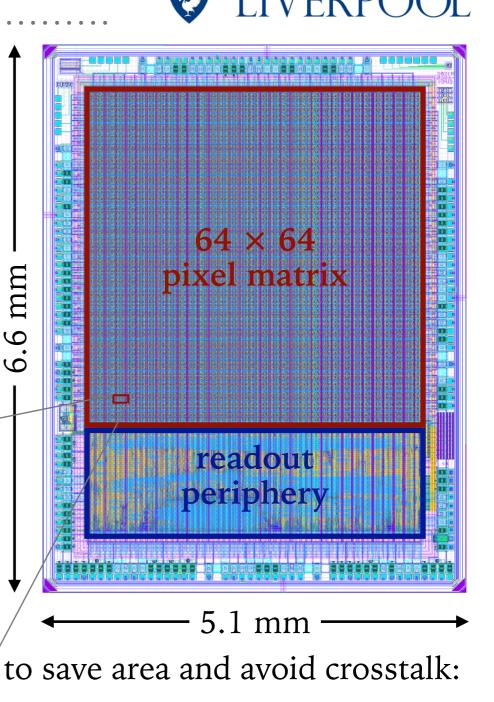

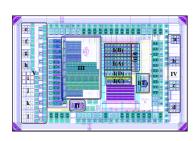

### **Design of RD50-MPW3**

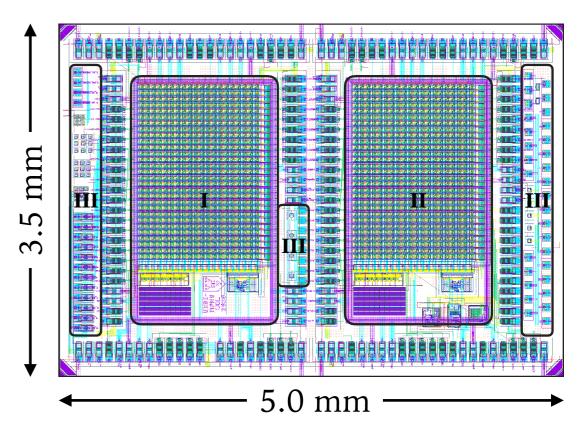

- RD50-MPW3 submitted in Dec. 2021, delivery expected in Jul. 2022.

- Composed of a 64 × 64 pixel matrix (by Liverpool) and a digital readout periphery (by HEPHY).

- Chip submission is lead by Liverpool.

- New features in RD50-MPW3 include:

- double-column architecture;

- advanced peripheral readout for high-rate data transmission.

UNIVERSIT

- Digital lines are shared within double column;

- Analog lines are shared by adjacent double columns.

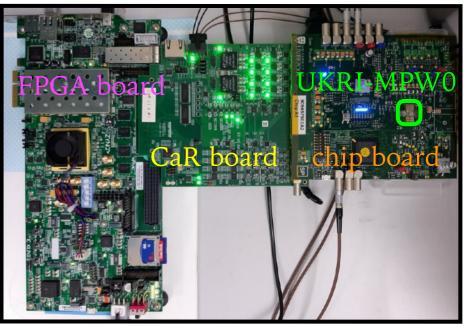

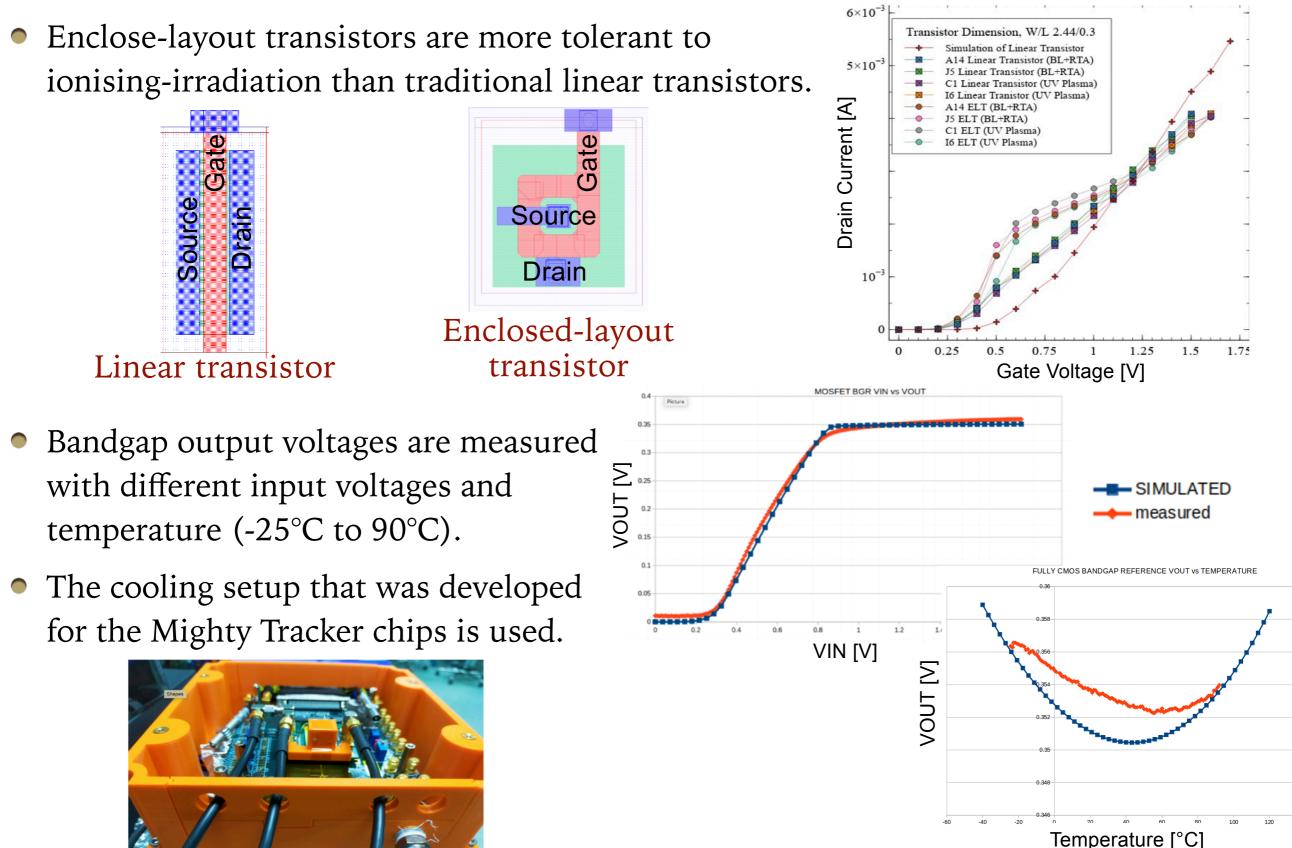

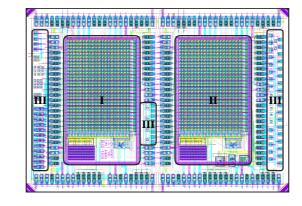

#### **UKRI-MPW0 Overview**

- UKRI-MPW0: a Liverpool internal project.

- Design by Liverpool during the 2020 lockdown.

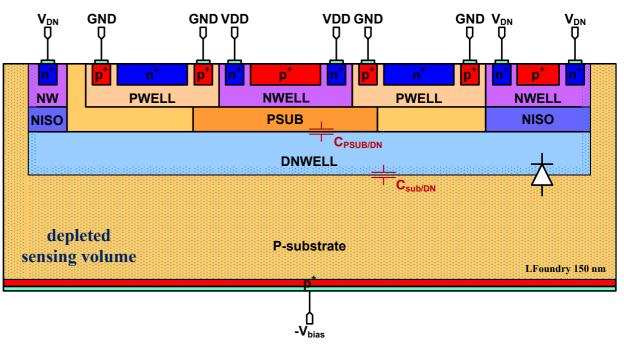

- First backside-only biased HV-CMOS for high breakdown -> better radiation tolerance.

- Two 20 × 29 pixel matrices (60  $\mu$ m × 60  $\mu$ m):

- I. Linear transistors

- II. Enclosed-Layout transistors (ELT)

- III. Test structures for I-V and Edge-TCT measurements, and characterise ELTs.

- Bandgap references and shunt regulator

- Two backside processing methods used:

- 1. Ion Implantation (BLII) + Rapid Thermal Annealing (RTA)

- 2. Plasma-Immersion Ion Implantation(PIII) + UV laser annealing

NIVERSIT

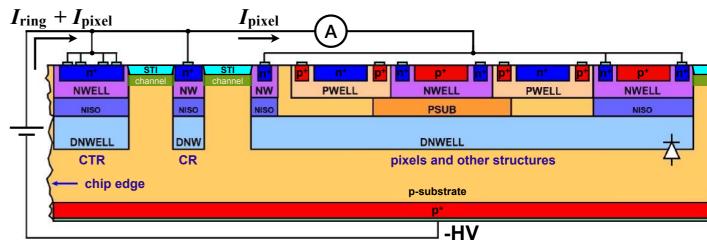

#### Backside-only high-voltage biasing

2021 HEP Annual Meeting, 2022/05/19-20, Chenfan

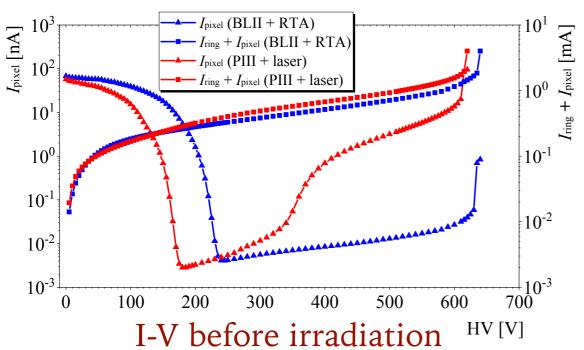

### **UKRI-MPW0 Initial Measurements: I-V**

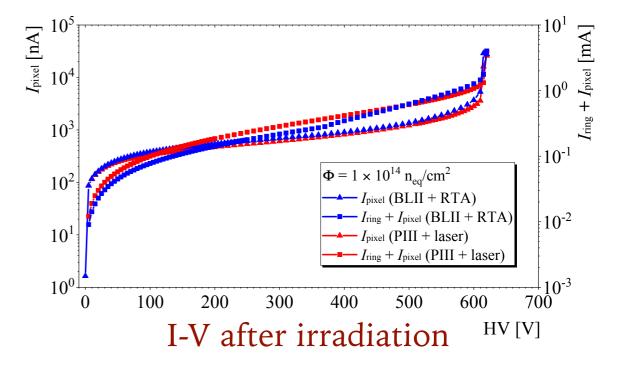

- I-V measurements on  $3 \times 3$

- $V_{BD} > 600$  V, significant import over the state of the art.

- Pixel leakage current  $I_{pixel}$  is unusual 'U' shape is due to the parasitic channel between ring and pixel.  $I_{rin}$

- Rings current is high, since they collect most leakage currents caused by edge defects.

- $V_{BD}$  still high after neutron irradiation.

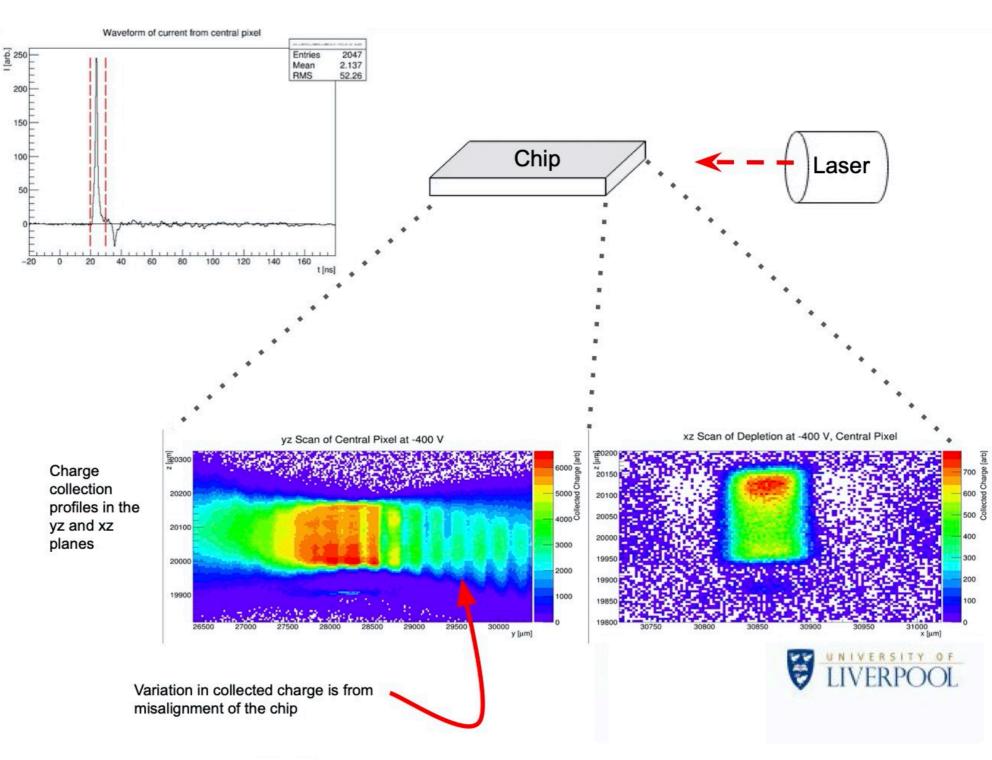

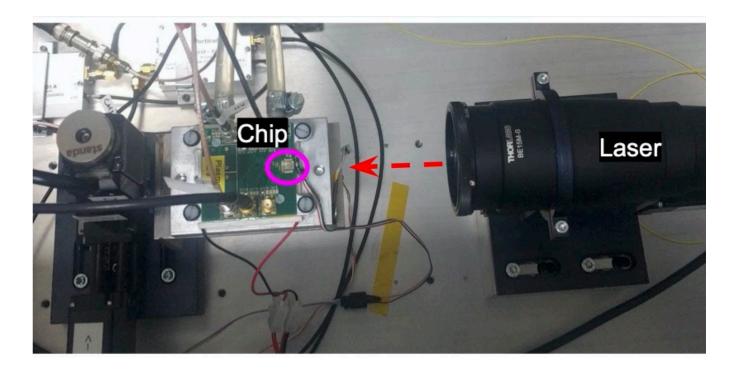

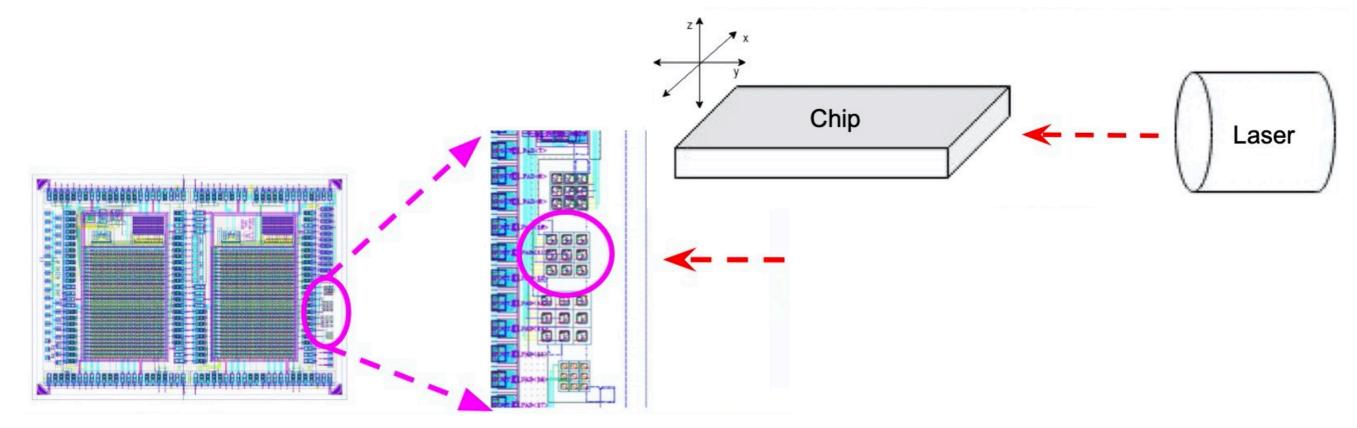

#### Edge-TCT measurement: Setup

- Edge-Transient Current Technique: focus IR laser inside the chip to generate free charges.

- Measure generated charges to study depletion depths (before and after irradiation).

- focus on test structures on chip edge.

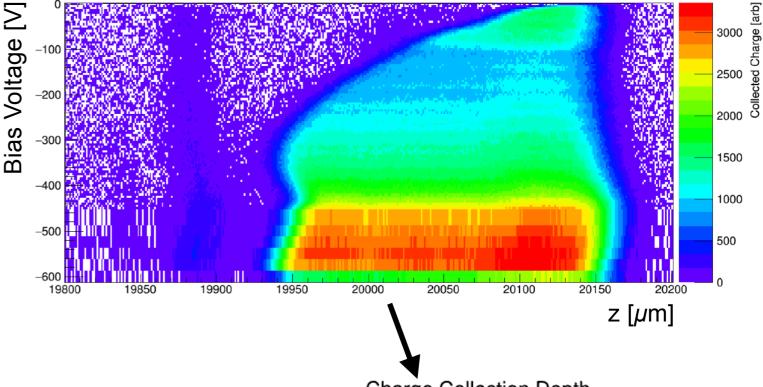

## **Edge-TCT measurement: Depletion Depth**

- Measure depletion depth for different bias voltages.

- Chip fully depletes at the bias voltage around 350 V.

- Full depletion depth is 200  $\mu$ m.

- Chip was thinned to 280  $\mu$ m. Investigating the difference.

FWHM of Charge Collection Area with Bias Voltage

Charge Collected In The Depletion Region With Reverse Bias

Charge Collection Depth

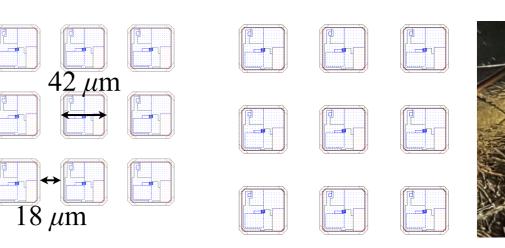

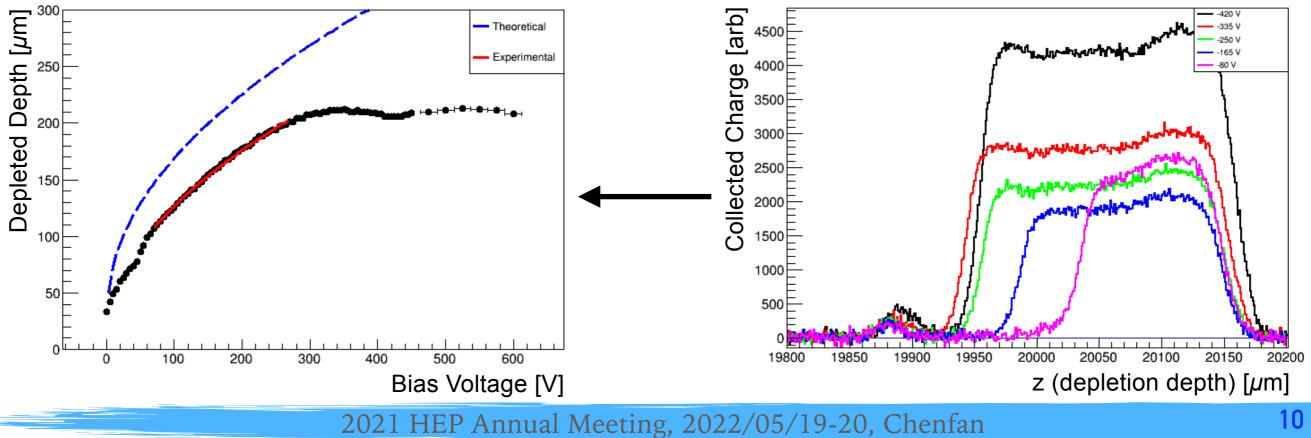

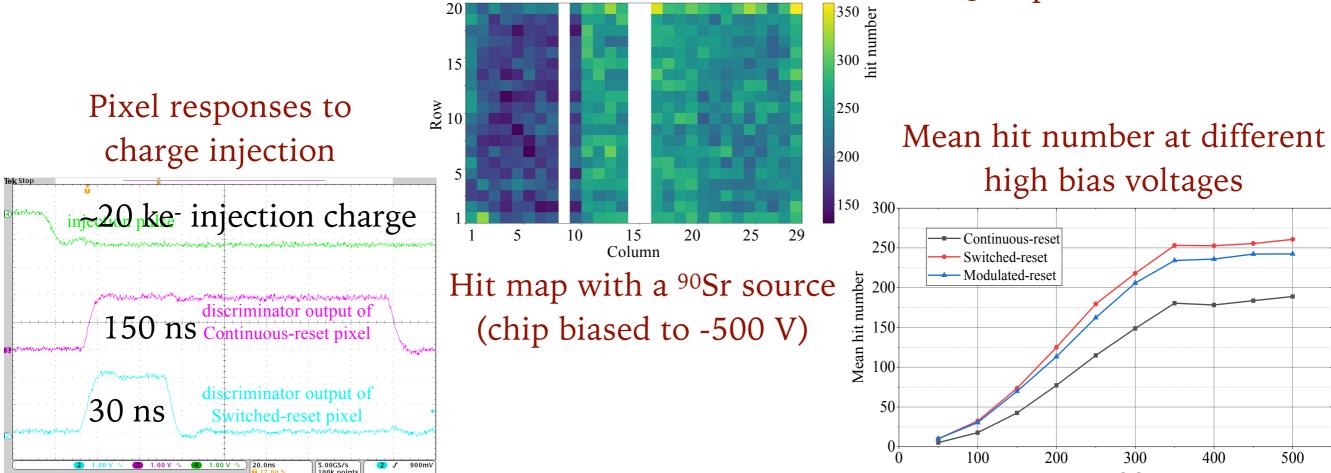

#### **Pixel Matrix Measurements**

- Measurements of the pixel matrices are going on.

- Each matrix contains 3 pixel flavours:

- 1. Continuous-reset pixel (column 1-10);

- 2. Switched-reset pixel (column 11-20);

- 3. Modulated-reset pixel (column 21-29).

- Pixel flavours 1. and 2. have been implemented in a previous prototype (RD50-MPW2).

DAQ for pixel matrices

Continuous-rese

Switched-reset

Modulated-reset

100

200

high bias voltages

300

HV [V]

400

2021 HEP Annual Meeting, 2022/05/19-20, Chenfan

500

### **Measurement of ELT and Bandgap**

#### Summary and Next step

- First beam test on RD50-MPW2.

- UKRI-MPW0 has unprecedented high breakdown voltage (> 600 V).

- More measurements are going on, beam test at CERN is planned.

- RD50-MPW3 has been designed and will be delivered and tested later this year.

- Planning to design UKRI-MPW1 to fix parasitic channels and high leakage current.

successful beam test

UKRI-MPW0

measurements are going on

# V).

UNIVERSITY

RD50-MPW3

#### Scan Procedure

- Laser induces current at beam wait in Silicon

- Waveform of current recorded and 10 ns window around peak integrated

- Chip moved incrementally moved in 3 dimensions charge collection recorded and mapped

- Used to find optimal x and y points in central pixel for depletion depth measurement